# Preamble

#### Last modified date: 2023-05-07

This document is an auto-generated version of the Draft SVP64 Specification available at

https://libre-soc.org/openpower/sv

for which the source code is available at

https://git.libre-soc.org/?p=libreriscv.git;a=tree;f=openpower;hb=HEAD

This PDF may be created with "make pdf" from the following file:

```

https://git.libre-soc.org/?p=libreriscv.git;a=blob;f=openpower/Makefile;hb=HEAD

```

by executing the following commands:

git clone https://git.libre-soc.org/git/libreriscv.git libresoc cd libresoc/libresoc/openpower make pdf

Simple-V Cray-style Vectors have been developed by the Libre-SOC Team, sponsored by the NLnet Foundation and NGI POINTER under EU Grants 871528 and 957073.

Simple-V is in DRAFT Status and will be submitted publicly (non-confidentially) through the OPF ISA WG "External Submissions" Process. Funding from NLnet, through their Privacy and Enhanced Trust Programme, requires full transparency.

As this document is under continuous rapid revision please check frequently at:

```

https://ftp.libre-soc.org/simple_v_spec.pdf

```

#### Contacts

For questions, comments, and clarification, please contact the following:

- Libre-SOC ISA Dev Mailing List libre-soc-isa@lists.libre-soc.org

- Luke Kenneth Casson Leighton Libre-SOC team lead and Red Semiconductor Ltd Director lkcl@lkcl.net

- David Calderwood Red Semiconductor Ltd Director djac@calderwoodhan.com

- Toshaan Bharvani OpenPOWER Foundation Technical Chair, VanTosh Director toshaan@vantosh.com

- Konstantinos Margaritis Engineer and Founder of VectorCamp, writing optimised assembler for a number of SIMD/Vector ISAs konstantinos@vectorcamp.gr

- Dmitry Selyutin Libre-SOC engineer, working on binutils SVP64 assembler ghostmansd@gmail.com

- Jacob Lifshay Libre-SOC engineer, CPU arch and verification programmerjake@gmail.com

- Cesar Strauss Libre-SOC engineer, CPU arch and verification cestrauss@gmail.com

- Andrey Miroshnikov Libre-SOC engineer, assisting with documentation andrey@technepisteme.xyz

#### **Executive Summary**

**Simple-V** is a Scalable Vector ISA Extension **specifically tailored** for the uniquely powerful capabilities of the Power ISA. **SVP64** is the instruction set format. We invented Simple-V to be simple because we don't like complicated.

Simple-V does not modify harm or corrupt the existing Power ISA and does not interfere with an existing system. It needs only a small allocation of opcodes (five) to implement, whereas any other Vector implementation would require an intrusive fundamental overhaul of the Power ISA.

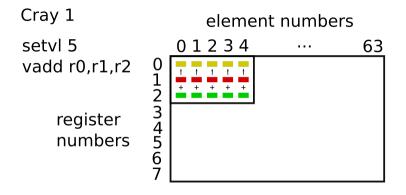

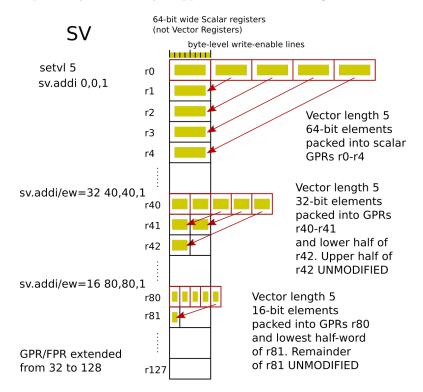

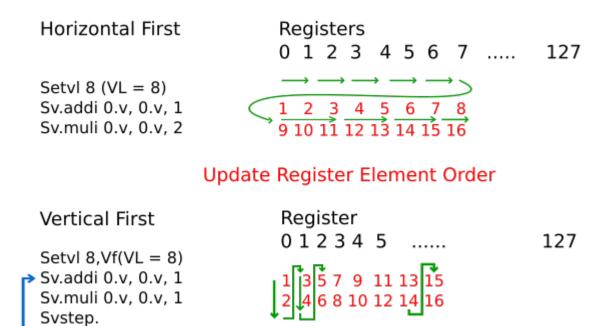

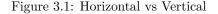

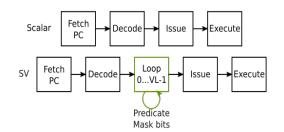

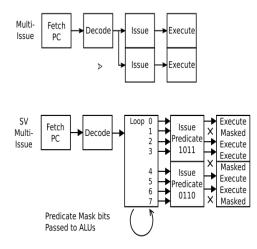

It is extremely important to think of Simple-V as a 2-Dimensional ISA: instructions vertical and registers horizontal otherwise it will be difficult to grasp and appreciate its RISC simplicity. Like all Cray-Style Scalable Vector ISAs, Simple-V binaries remain ubiquitous, the ISA uniform. The Compliancy Levels offer a means to scale up in complexity to meet the target application requirements.

- GPUs may implement massive-wide SIMD back-ends, focussing on number-crunching.

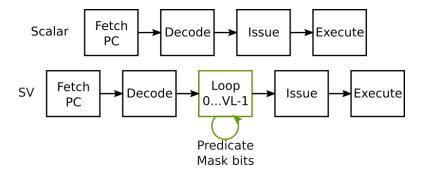

- Existing Multi-issue Superscalar implementations may insert Simple-V between decode and issue with minimal disruption.

- Single-issue in-order implementations are very straightforward.

- Inter-core communication (OpenCAPI, other) may still be utilised because SVP64 fundamentally remains and respects the Power ISA.

All implementations regardless of back-end capability may execute the exact same binaries (this is known to be extremely important to the Power ISA ecosystem). If not done as carefully as SVP64, the addition of any other Scalable Vector Extension would require a significant number of opcodes, putting further pressure on Major Opcode space which was never designed with Scalable Vectors in mind. Contrast with RISC-V which was designed over a 7 year period with Cray-style Vectors right from the start.

Even with this amount of time spent, SVP64 exceeds the capability of RVV. RISC-V could have been significantly enhanced if Simple V had been applied to it: this possibility was investigated very early but the decision was made to go with Power ISA instead.

Therefore it is crucial to note that Simple-V is **not RISC-V and is not RISC-V Vectors**. NEC SX Aurora, RVV, Simple-V and MRISC32 are all based on Cray-style Scalable Vectors of 50 years ago, hence the similarity, the provision of a **setvl** instruction, and why they are each called "Scalable" Vectors, because it is the **setvl** instruction that presents the **programmer** with explicit control over Vector length.

VSX and NEON are PackedSIMD, and AVX-512 and ARM SVE2 are Predicated SIMD ISAs. None of them provide Scalability to the Programmer. SVE2 is Silicon Scalable, not Programmer Scalable: the distinction is profoundly important (already causing problems). For Predicated SIMD, Programmers must emulate Cray-style scaling through explicit predicate masking, which increases instruction count in hot-loops.

#### description, URL

Unit tests and simulator for Power ISA v3.0 and SVP64 https://git.libre-soc.org/?p=openpower-isa.git;a=tree;f=src/openpower/decoder/isa;hb=HEAD pypowersim tutorial https://libre-soc.org/docs/pypowersim/ several thousand more ISA unit tests https://git.libre-soc.org/?p=openpower-isa.git;a=tree;f=src/openpower/test;hb=HEAD demo, showing 4.5x reduction in program size for MP3 decode, greatly simplifies assembler development https://git.libre-soc.org/?p=openpower-isa.git;a=tree;f=media/audio/mp3;hb=HEAD binutils support for DRAFT SVP64 (now upstream) https://git.libre-soc.org/?p=binutils-gdb.git;a=shortlog;h=refs/heads/svp64-ng

| WYR         1         North         1         North         1         North         1         North         1         North         North <t< th=""><th>21 yes<br/>no<br/>yes<br/>yes<br/>yes<br/>see<sup>37</sup><br/>see<sup>37</sup></th><th>yes 4 no</th><th>no 5<br/>ves 14</th><th>ODS</th><th>int</th><th>F/First</th><th>Data-dep<br/>F-first</th><th>Pred<br/>Result</th><th>HW<br/>Matrix</th><th>DCT<br/>FFT</th></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21 yes<br>no<br>yes<br>yes<br>yes<br>see <sup>37</sup><br>see <sup>37</sup>                                                                                                                                         | yes 4 no                                                     | no 5<br>ves 14                                                  | ODS                                         | int                                        | F/First                                           | Data-dep<br>F-first                                    | Pred<br>Result                             | HW<br>Matrix                           | DCT<br>FFT        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------|--------------------------------------------|---------------------------------------------------|--------------------------------------------------------|--------------------------------------------|----------------------------------------|-------------------|

| (5X 700+ 700?13 PackedSIMD yes no<br>NVE2 -350 <sup>16</sup> 7088 <sup>17</sup> PackedSIMD yes no<br>NVE2 -1000 <sup>25</sup> 7266 <sup>26</sup> PredSIMD <sup>21</sup> NO 22 no 2<br>NVX 2 <sup>83</sup> -1002 <sup>29</sup> -25000 <sup>30</sup> Scalable <sup>31</sup> NO 22 yes<br>Nurora5X <sup>33</sup> -200 <sup>34</sup> unknown <sup>35</sup> Scalable <sup>36</sup> yes yes<br>yes<br>5600 <sup>37</sup> -200 unknown <sup>35</sup> Scalable <sup>36</sup> yes yes yes<br>sec <sup>31</sup> here are failer than and designed badly, the 24-bit Pre-<br>specific operations. See {SVP64 Augmentation Table} for full list.<br>P64 Vectorises a Vector sorreept on top of the Scalar insistent insistent on the specific operations. See {SVP64 Augmentation Table} for full list.<br>P64 Vectorises a Vector sorreept on top of the Scalar GPR, FPR and<br>specific operations. See {SVP64 Augmentation Table} for full list.<br>P64 Vectorises a Vector sorreept on top of the Scalar GPR, FPR and<br>specific operations. See {SVP64 Augmentation Table} for full list.<br>P64 Vectorises a Vector sorreept on top of the Scalar GPR, FPR and<br>specific operations. See {SVP64 Augmentation Table} for full list.<br>P64 Vectorises a Vector sorreept on top of the Scalar GPR, FPR and<br>specific operations. See {SVP64 Augmentation Table} for full list.<br>P64 Vectorises a Vector sorreept on top of the Scalar GPR, FPR and<br><i>S</i> T Fault-First: see {SVP64 Augmentation Table} for full list.<br>P64 Vectorises a Vector sorreept on top of the Scalar GPR, FPR and<br><i>S</i> T (Lee) and FFT Full Triple-loops supported, RADIX2-only. Non-<br>ture-dependent Fail-First: Based on LD/ST Fail-first, extended to da<br>defeate-result effectively turns any standard op into a type of "cmp<br><i>N</i> states that escalability asist" (MMA) which due<br>fill to exactly ascertain, see ARM Architecture Reference Manua<br>B (S Vector Registers are mis-maned: they are 100% PackedSIMD.<br>Were SSA v3.1 contains "Matrix Multiply Assist" (MMA) with due<br>defeate-result fiftcutisc, SVE2 1000 intrinsics.<br>SON 32-bit 2754 intrinsics, NED 0, 94 bit intrinsics.<br>Sol 32-bit section are stand-alone, i.e. like SVE2, and AVX, and<br>At states that the Scalability is a slitcorn and any balle Matrix Optional B Autrix Optional B A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                     | ou                                                           | ves 14                                                          | see 6                                       | yes <sup>7</sup>                           | yes <sup>8</sup>                                  | yes <sup>9</sup>                                       | yes 10                                     | yes <sup>11</sup>                      | ves <sup>12</sup> |

| <ul> <li>(EON -250<sup>16</sup> 7088 <sup>17</sup> PackedSIMD yes no 22000<sup>19</sup> 6040 <sup>20</sup> PredSIMD yes no 22756.</li> <li>(VE22 -1000s<sup>23</sup> 7256.</li> <li>(VZ51224 -1000s<sup>23</sup> 2250.</li> <li>(VZ51224 -1000s<sup>23</sup> 220034 unknown<sup>35</sup> Scalable<sup>36</sup> yes yes 6000<sup>37</sup> -200 unknown AutoVec<sup>37</sup> yes see 3</li> <li>(MZ51224 -1000s<sup>26</sup> -200 unknown AutoVec<sup>37</sup> yes yes 5000<sup>37</sup> -200 unknown AutoVec<sup>37</sup> yes yes 6000<sup>37</sup> Yes 4000 Yes 7000 Yes 6000 Yes 4000 Yes 700 Yes 4000 Yes 700 Yes 7000 Yes 7000 Yes 700 Yes 700 Yes 700 Yes 700 Yes 700 Yes 700 Yes 7000 Yes 700 Yes 70</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                     |                                                              | 201                                                             | yes                                         | no                                         | no                                                | no                                                     | no                                         | $^{\rm yes}$ 15                        | , ou              |

| <ul> <li>VE2 -1000<sup>19</sup> 6040<sup>20</sup> PredSIMD<sup>21</sup> NO <sup>22</sup> no <sup>2</sup>/v85</li> <li>VX512<sup>24</sup> -1000<sup>25</sup> 726<sup>56</sup> PredSIMD v85</li> <li>v8600<sup>37</sup> -100<sup>23</sup> 2500<sup>30</sup> Scalable<sup>36</sup> v985 w08</li> <li>urors2X<sup>33</sup> -200<sup>34</sup> unknown <sup>35</sup> Scalable<sup>36</sup> v985 w08</li> <li>6000<sup>37</sup> -200</li> <li>unknown AutoVec<sup>37</sup> v985 w08</li> <li>6000<sup>37</sup> -200</li> <li>unknown AutoVec<sup>37</sup> v985 w08</li> <li>6000<sup>37</sup> -200</li> <li>unknown AutoVec<sup>37</sup> v985 w08</li> <li>8 EXT001 24-bit prefixing using 25% of EXT001 space. See {SVP6</li> <li>s EXT001 24-bit prefixing using 25% of EXT001 space. See {SVP6</li> <li>reated as a 1-Dimensional ISA, and designed badly, the 24-bit Presigned well, there are far less. N prefix intrinsics plus M scalar init</li> <li>2 Dimensional Scalable Vector ISA specifically designed for the specific operation. See {SVP64 Appendix} and ARM SVE Fault-First.</li> <li>2 Dimensional Scalable Vector ISA specifically designed for the specific operation. See {SVP64 Appendix} and ARM SVE Fault-First.</li> <li>2 Dimensional Scalable Vector ISA specifically designed for the specific operation. See {SVP64 Appendix} and ARM SVE Fault-First.</li> <li>2 Dimensional Scalable Vector ISA specifically designed for the specific operation. See {SVP64 Appendix} and ARM SVE Fault-First.</li> <li>2 Dimensional Scalable Vector ISA specifically designed for the specific operation. See {SVP64 Appendix} and ARM SVE Fault-First.</li> <li>2 Dimensional Scalable Vector ISA specifically designed for the specific operation. See {SVP64 Appendix} and ARM SVE Fault-First.</li> <li>2 Dimensional Scalable Vector ISA specifically designed for the specific operation. See {SVP64 Appendix} and ARM SVE Fault-First.</li> <li>2 Dimensional Scalable Vector ISA Static the sector motion option option</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                     | ou                                                           | yes                                                             | see 18                                      | ou                                         | ou                                                | ou                                                     | no                                         | ou                                     | ou                |

| <ul> <li>VX512<sup>24</sup> -1000<sup>529</sup> -2560<sup>30</sup> Scalable<sup>31</sup> NO <sup>22</sup> yes unconsX<sup>33</sup> -200<sup>34</sup> unknown <sup>35</sup> Scalable<sup>36</sup> yes <sup>36</sup> yes <sup>36</sup></li></ul> |                                                                                                                                                                                                                     | ou                                                           | yes                                                             | see 18                                      | ou                                         | yes <sup>8</sup>                                  | no                                                     | no                                         | $yes^{23}$                             | ou                |

| XVX - 2003 unknown 35 Scalable <sup>36</sup> yes yes acoustic scalable of the Scalable vector 25003 unknown 35 Scalable <sup>36</sup> yes yes acoust with the substraint of the state of the st                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                     | no                                                           | yes                                                             | see <sup>18</sup> 32                        | ou                                         | ou                                                | ou                                                     | no                                         | yes <sup>21</sup>                      | ou                |

| g000 <sup>37</sup> -200 unknown AutoVec <sup>37</sup> yes ges g000 <sup>37</sup> -200 unknown AutoVec <sup>37</sup> yes ges governers200 unknown AutoVec <sup>37</sup> yes ges governers at a 1-Dimensional ISA, and designed badly, the 24-bit Presigned well, there are far less. N prefix intrinsics plus M scalar instances plus for the specific operations. See {SVP64 Augmentation Table} for this precisional Scalable Vector ISA specifically designed for the specific operations. See {SVP64 Augmentation Table} for this precisional Scalable Vector ISA specifically designed for the specific operations. See {SVP64 Augmentation Table} for this prefixers are destroad as a 1-Dimensional Scalable Vector ISA specific operations. See {SVP64 Augmentation Table} for this prefixers are dependent Pail-First: Based on LD/ST Pail-first, extended to da dicate-result effectively turns any standard op into a type of "cmp v non-power-of-two Matrices up to 127 FMACs or other FMA-style vecor integer add is just v. adde. For optimal performance Bigint Mul at YS SY Statinsics, contains links to additional VSX intrinsics for 1 (Lee) and FFT Full Triple-loops supported, RADIX2-only. Norn FV core gen interfaces, contains links to additional VSX intrinsics for 1 (Lee) and FFT Full Triple-loops supported, RADIX2-only. Norn FV core grait intrinsics. NBON 64-bit 4334 intrinsics on NO 32-bit to accertain, see NEON/FP. Critically depends on ARM Sc for the sective are the scalability is a Silicon-partner choice. Scalability to accertain, see ARM Architecture Reference Manua E 4140 intrinsics. SVE2 J000 intrinsics. NBON SVE2, and AVX, unlike to exactly ascertain, see ARM Architecture Reference Manua E 4140 intrinsics. SVE2 J000 intrinsics and instruction are instruction and infinult to exactly ascertain, see ARM Architecture Reference Manua E 4140 intrinsics. SVE2 J000 intrinsics and the scalability is a Silicon-partner choice. Scalability as a Silicon-partner choice. Scalability is a Silicon-partner choice. Scalability is a Silicon-partner ordin subsets. Critically depends on J unt includes SSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                     | ou                                                           | yes                                                             | yes 22                                      | no                                         | yes                                               | ou                                                     | no                                         | no<br>2                                | ou                |

| s EXT001 24-bit prefixing using 25% of EXT001 space. See {SVP6<br>reated as a 1-Dimensional ISA, and designed badly, the 24-bit Prefix<br>gined well, there are fare lass. N prefix intrinsics plus M scalar inst-<br>Dimensional Scalable Vector ISA <b>specifically designed for the</b><br>specific operations. See {SVP64 Augmentation Table} for full list.<br>P64 Vectorises Scalar ops. It is up to the implementor to choose<br>integer add is just av adde. For optimal performance Bigin Mula<br>ST Fault-First: Based on LD/ST Fail-first, extended to da<br>dicate-result effectively turns any standard op into a type of "cmp<br>rom-power-of-two Matrices up to 127 FMACs or other FMA-style<br>rom-power-of-two Matrices up to 127 FMACs or other FMA-style<br>rom-power of the standard op into a type of "cmp<br>rom-power of the standard op into a type of "cmp<br>rom-power of the standard op into a type of "cmp<br>rom rom et additional VSX intrinsics for 1<br>K's Vector Registers are mis-nance: they are 100% PastedSIMD.<br>ver ISA v3.1 contains "Matrix Multiply Assist" (MMA) which due<br>cult to exactly accrtain, see NEM Architecture Reference Manua<br>S: 4140 intrinsics, SVE2 1900 intrinsics<br>for unit to exact the scalability is a Silicon-partner choice. Scalabil<br>mure difficulties, quote "you may be stuck with only using thil<br>inter difficulties on the "you may be stuck with only using the<br>icult to exactly accrtain, see NEM Architecture Reference Manua<br>S: 4140 intrinsics, SVE2 1900 intrinsics<br>for the to exactly accrtain, see NEM Architecture Reference Manua<br>S: 4140 intrinsics, SVE2 1900 intrinsics<br>for the cos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                     | ou                                                           | yes<br>see <sup>37</sup>                                        | ou                                          | $_{\rm yes^{38}}$                          | $_{\rm see}^{\rm no}$                             | no                                                     | ou                                         | ou                                     | ou                |

| igned well, there are far less. N predix intrinsics plus M scalar inst<br>specific operations. See (SVP64 Augmentation Table) for full list.<br>P64 provides a Vector concept on top of the Scalar GPR, FPR an<br>P64 Vectorises Scalar ops. It is up to the implementor to choose<br>-integer add is just wadds. For optimal performance Bigint Mul al<br>ACT Fault-First: See (SVP64 Appendix) and ARM SVE Fault-First<br>acdependent Fail-First: Based on LD/ST Fail-first, extended to dis<br>dicate-result effectively turns any standard op into a type of "cmp<br>v non-power-of-two Matrices up to 127 FMACs or other FMA-style<br>v non-power-of-two Matrices up to 127 FMACs or other FMA-style<br>v non-power-of-two Matrices up to 127 FMACs or other FMA-style<br>v non-power-of-two Matrices up to 127 FMACs or other FMA-style<br>v con-power-of-two Matrices up to 127 FMACs or other FMA-style<br>v con-power-of-two Matrices up to 127 FMACs or other FMA-style<br>v con-power-of-two Matrices up to 127 FMACs or other FMA-style<br>v constants "Matrix Multiply Assist" (MMA) which due<br>to 000 32-bit in NEON (S-bit 4334 intrinsics for 1<br>X's Vector Registers may be 128-bit in NEON, SVE2, and AVX, unlike<br>foult to ascertain, see NEON/VFP. Critically depends on AMA states<br>to 000 32-bit 2754 intrinsics. NEON (S-bit 4334 intrinsics.<br>hough registers may be 128-bit in NEON, SVE2, and AVX, unlike<br>foult to exactly ascertain, see ARM Architecture Reference Manua<br>E: 4140 intrinsics. SVE2 1900 intrinsics<br>More attick calability is a Silicon-partner choice. Scalabil<br>mer difficulties. quote "you may be stuck with only using th<br>licon-Partner" Scaling achieved through allowing same instruction<br>lable Matrix Optional Extension outer-product instructions SMOF<br>7512 Wilebedia, Lifecycle of an instruction set including full slude<br>icult to exactly ascertain, contains subsets. Critically depends on 1<br>ant includes SSE, SSE2, AVX, AVX, and all AVX512 variants<br>varianced matrix Extensions supports BF16 and INT8 only. Separate<br>V intrinsics listing page is 25,001 lines long.<br>W offerc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | VP64 Chapter}<br>Prefix expands 200+ scalar instructions to well over a million intrinsics (N~=10^4 <b>times</b> M~=10^2). If treated as a 2-Dimensional ISA                                                        | scalar instru                                                | Letions to we                                                   | il over a mill                              | ion intrinsic                              | $(N^{-10^{-4}})^{-10^{-4}}$                       | times M~=10                                            | ~2). If treate                             | ed as a 2-Di                           | mensio            |

| integer add is just wadde. For optimal performance Bigint Mul al<br>(ST Fault-First: see [SVP64 Appendix) and ARM SVE Fault-First<br>adopendent Fail-First: Based on LD/ST Fail-first, extended to da<br>idicate-result effectively turns any standard op into a type of "cmp<br>r non-power-of-two Matrices up to 127 FMACs or other FMA-style<br>T (Lee) and FFT Full Triple-loops supported, RADIX2-only. Norn<br>vere gor intrinsics, contains links to additional VSX intrinsics for 1<br>VS Vector Registers are mis-named: they are 100% PackedSIMD.<br>Vere Station and Strink Multiply Assist" (MMA) which due<br>ere ISA v3.1 contains "Matrix Multiply Assist" (MMA) which due<br>to a scertain, see NEON/VFP. Critically depends on ARM Sc<br>ON 32-bit 2754 intrinsics, NEON 64-bit 4334 intrinsics.<br>J 4140 intrinsics, SVE2 1900 intrinsics<br>and pregisters may be 128-bit in NEON, SVE2, and AVX, unlike<br>(cult to exactly ascertain, see ARM Architecture Reference Manual<br>3.4140 intrinsics, SVE2 1900 intrinsics<br>M states that the Scalability is a Silicon-partner choice. Scalabil<br>inter difficulties, quote "you may be stuck with only using th<br>inter difficulties. Under state and a NX512 variants<br>are difficulties. Lifecycle of an instruction set including full slide:<br>(cult to exactly ascertain, contains subsets. Critically depends on<br>in the culter oracity ascertain, contains subsets. Critically depends on<br>in the culter oracity ascertain, contains subsets. Critically depends on<br>in the culter stand-alone, i.e. like SVE2 and AVX-512 variants<br>are deal matrix Extensions supports BF16 and INT8 only. Separate<br>V spec<br>C-V Vectors are not stand-alone, i.e. like SVE2 and AVX-512 variants<br>are the original Cray RVV is a truly scalable Vector ISA (Cray sett<br>does not have. The RISC-V Founders strongly discourage efforts<br>event at the settion due strongly discourage offorts<br>are the original Cay RVV is a truly scalable Vector ISA (Cray sett<br>does not have. The RISC-V Founders strongly discourage offorts<br>are to a strongly as strongly discourage offorts<br>are the original Cay RVV is a truly scalable Vect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | the Power ISA with both Horizontal-First and Vertic:<br>list. Key: 2P - Twin Predication, 1P - Single-Predicate<br>t and CR Fields, extended to 128 entries.<br>ose (optionally) whether to apply SVP64 to e.g. VSX | both Horizc<br>Predication,<br>nded to 128<br>ther to appl.  | ontal-First a<br>1P - Single-<br>entries.<br>y SVP64 to         | nd Vertical-F<br>Predicate<br>e.g. VSX Que  | irst Modes.<br>ad-Precision                | See {Vector<br>1 (128-bit) in                     | · ISA Comparis<br>istructions, to                      | ion}<br>create 128-bi                      | t Vector op                            | ż                 |

| dicate-result effectively turns any standard op into a type of "cmp<br>non-power-of-two Matrices up to 127 FMACs or other FMA-style<br>T (Lee) and FFT Full Triple-loops supported, RADIX2-only. Non<br>vec gcc intrinsics, contains links to additional VSX intrinsics for 1<br>vs Vector Registers are mis-named: they are 100% PackedSIMD.<br>ver ISA v3.1 contains "Matrix Multiply Assist" (MMA) which due<br>cult to ascertain, see NEON/VFP. Critically depends on ARM Sc<br>20 32-bit 2754 intrinsics, NEON 64-bit 4334 intrinsics.<br>ongh registers may be 128-bit in NEON, SVE2, and AVX, unlike<br>cult to ascertain, see ARM Architecture Reference Manual<br>3: 4140 intrinsics, SVE2 1900 intrinsics<br>incomp registers may be 128-bit in NEON, SVE2, and AVX, unlike<br>cult to exactly ascertain, see ARM Architecture Reference Manual<br>3: 4140 intrinsics, SVE2 1900 intrinsics<br>M states that the Scalability is a Silicon-partner choice. Scalabil<br>iner difficulties: quote "you may be stuck with only using th<br>ionor-Pattner" Scalability is a Silicon-partner choice. Scalabil<br>incompartner" Scalability is a Silicon-partner choice. Scalabil<br>incompartner accult a secterain, ascertain, sensets. Critically depends on<br>1 alble Matrix Optional Extension outer-product instructions SMOF<br>8512 Wikipedia, Lifecycle of an instruction set including full silde<br>cult to exactly ascertain, contains subsets. Critically depends on<br>1 and includes SSE, SSE2, AVX, AVX2 and all AVX512 variants<br>acced matrix Extension supports BF16 and INT8 only. Separate<br>V spec<br>C-V Vectors are not stand-alone, i.e. like SVE2 and AVX-512 are<br>visced matrix Extension Supports BF16 and INT8 only. Separate<br>visced matrix Extension supports BF16 and CVT-3 visced<br>visced matrix Extension suports BF16 visced visced visced<br>vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nd divide first req.<br>st<br>uta. Truncates VL                                                                                                                                                                     | uire additior<br>based on fa                                 | n of two scal<br>iling Rc=1 t                                   | ar operations<br>est. Similar t             | s (in turn, n<br>to Z80 CPIF               | aturally Vec<br>3. See {SVP                       | torised by SVF<br>64 Appendix}                         | 64). See {Bi                               | g Integer A                            | nalysis           |

| If (Lee) and FYT Full Tirple-loops supported, HADJX2-only, Norwee gcc intrinsics, contains links to additional VSX intrinsics for 11 vec gcc intrinsics, contains "Matrix Multiply Assist" (MMA) which due cult to ascertain, see NEON/VFP. Critically depends on ARM Sci 203 32-bit 2754 intrinsics, NEON 64-bit 4334 intrinsics. Int of a scentain, see NEON/VFP. Critically depends on ARM Sci 203 32-bit 2754 intrinsics, NEON 64-bit 4334 intrinsics. Int of a scentain, see NEON/VFP. Critically depends on ARM Sci 203 32-bit 2754 intrinsics, NEON 64-bit 4334 intrinsics. Int of a scentain, see NEON/VFP. Critically depends on ARM Sci 203 32-bit 2754 intrinsics. Int a scentain, see ARM Architecture Reference Manual S: 4140 intrinsics, SVE2 1900 intrinsics Matates that the Scalability is a Silicon-partner choice. Scalabilities (non-partner % of the only using th incomparative "Scaling achieved through allowing same instructions SMOF 8512 Wikipedia, Lifecycle of an instruction set including full slide cult to exactly ascertain, contains subsets. Critically depends on 1 ut includes SSE, SSE2, AVX, AVX2 and all AVX512 variants are acceded matrix Extension supports BF16 and INT8 only. Separate V Spec C-V Vectors are not stand-alone, i.e. like SVE2 and AVX-512 are viruly scalable Wetch TSA (Cray settruct does not have. The RISC-V Founders strongly discourage efforts eventives all algorithms to contains a loop construct does not have. The Laboration strongly discourage efforts event.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ". See {SVP64 Ap<br>op including Ter                                                                                                                                                                                | pendix}<br>nary Logical                                      | l, full triple-l                                                | oop Schedule                                | . See {REN                                 | AAP subsyst                                       | em}                                                    |                                            |                                        |                   |

| X's Vector Registers are mis-named: they are 100% PackedSIMD. Are 10.0 and 10 and 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nally only found in<br>SA 2.05/6/7, 3.0 a                                                                                                                                                                           | n VLIW DSE<br>and 3.1                                        | ASM II.) s4                                                     | 320, Qualcom                                | . Hexagon).                                | See { KEMA                                        | P subsystem }                                          |                                            |                                        |                   |

| ON 32-bit 2754 intrinsics, NEON 64-bit 4334 intrinsics.<br>hough registers may be 128-bit in NEON, SVE2, and AVX, unlike<br>icult to exactly ascretian, see ARM Architecture Reference Manual<br>8: 4140 intrinsics, SVE2 1900 intrinsics<br>Ma states that the Scalability is a Silicon-partner choice. Scalabil<br>mer difficulties, quote "you may be stuck with only using th<br>icon-Partner" Scaling achieved through allowing same instruction<br>ble Matrix Optional Extension outer-product instructions SMOP<br>X512 Wikipedia, Lifecycle of an instruction set including full slide<br>icult to exactly ascritain, contains subsets. Critically depends on 1<br>un includes SSE, SSE2, AVX, AVX2 and all NVX512 variants<br>arced matrix Extensions supports BF16 and INT8 only. Separate<br>V Spec<br>Ci-V Vectors are not stand-alone, i.e. like SVE2 and AVX-512 are<br>Virtnisics listing page is 55,000 lines long.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | D. AVX-512 is not a<br>lue to PackedSIMD is<br>Scalar instructions                                                                                                                                                  | Vector ISA e<br>s restricted t                               | either. See F<br>to RADIX2 t                                    | 'lynn's Taxon<br>and requires i:            | lomy<br>nline assem                        | bler loop-um                                      | rolling for non-                                       | power-of-twc                               | Matrix din                             | nensior           |

| ciult to exactly ascertain, see ARM Architecture Reference Manual<br>3: 4140 intrinsics. SVE2 1900 intrinsics<br>Mi states that the Scalability is a Silicon-partner choice. Scalabili<br>mer difficulties. quote "you may be stuck with only using th<br>icon-Partner" Scaling achieved through allowing same instruction<br>lable Matrix Optional Extension outer-product instructions SMOP<br>7512 Whiledia, Lifecycle of an instruction set including full slide<br>(cult to exactly ascertain, contains subsets. Critically depends on 1<br>un fincludes SSE, SSE2, AVX, AVX, and all AVX512 variants<br>anced matrix Extensions supports BF16 and INT8 only. Separate<br>V 59ec<br>C-V Vectors are not stand-alone, i.e. like SVE2 and AVX-512 are<br>V intrinsics listing page is 25,000 lines long.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VSX there are ver                                                                                                                                                                                                   | ry few (or no                                                | o) actual arit                                                  | thmetic 128-b                               | it operation                               | ns. Only RV                                       | V and SVP64 ]                                          | nave the poss                              | ibility of 12                          | 8-bit c           |

| M states that the Scalability is a Silicon-partner choice. Scalabiliume difficulties: quote "you may be stude with only using the libble Matrix Optional Extension outer-product instruction SMOP 5512 Wikipedia, Lifecycle of an instruction set including full slide: to exactly ascertain, contains subsets. Critically depends on 1 ut includes SSE, SSE2, AVX, AVX2 and all AVX512 variants anced matrix Extensions supports BF16 and INT8 only. Separate V Spec C-V Vectors are not stand-alone, i.e. like SVE2 and AVX-512 are visual according page is 25,000 lines long.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | l Supplement, DD                                                                                                                                                                                                    | I 0584. Criti                                                | ically depend                                                   | ds on ARM S                                 | calar instru                               | ctions.                                           |                                                        |                                            |                                        |                   |

| ST12 When you have a subset of an instruction set including that subsets in the control of the set of the s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ity in the ISA is<br>e bottom 128 bi<br>to act on different                                                                                                                                                         | not availat<br>its of the v<br>regfile size                  | ector, or n<br>and bitwidt                                      | programmer<br>eed to code<br>h. This catast | specifically<br>trophically                | y for each inst<br>results in bir                 | width"<br>width"<br>nary non-interc                    | 32, which is<br>perability.                | already cau                            | sing a            |