# RFC ls010 Simple-V Zero-Overhead Loop Prefix Subsystem </>

- Funded by NLnet under the Privacy and Enhanced Trust Programme, EU Horizon2020 Grant 825310, and NGI0 Entrust No 101069594

- https://www.sigarch.org/simd-instructions-considered-harmful/

- https://libre-soc.org/openpower/sv/

- https://libre-soc.org/openpower/sv/rfc/ls010/

- https://bugs.libre-soc.org/show\_bug.cgi?id=1056

- https://git.openpower.foundation/isa/PowerISA/issues/64

- https://git.openpower.foundation/isa/PowerISA/issues/122

- https://libre-soc.org/openpower/sv/ls010/trial\_addi/

- https://libre-soc.org/openpower/sv/ls010/hypothetical\_addi/

#### Severity: Major

Status: New

Date: 04 Apr 2023. v2 TODO

#### Target: v3.2B

Source: v3.1B

#### Books and Section affected:

New Book: new Zero-Overhead-Loop New Appendix, Zero-Overhead-Loop

#### Summary

Adds a Zero-Overhead-Loop Subsystem based on the Cray True-Scalable Vector concept in a RISC-paradigm fashion. Total instructions six 5-bit XO, plus Prefix format (PO9).

#### **Submitter**: Luke Leighton (Libre-SOC)

**Requester**: Libre-SOC

#### Impact on processor:

Addition of new "Zero-Overhead-Loop-Control" DSP-style Vector-style subsystem that in simple low-end (Embedded) systems may be minimalistically and easily be implemented by inserting a new fully-independent Pipeline Stage in between Decode and Issue, with very little disruption, and in higher performance pre-existing Multi-Issue Out-of-Order systems seamlessly fits likewise to significantly boost performance.

#### Impact on software:

Requires support for new instructions in assembler, debuggers, and related tools. Dramatically reduces instructions. Requires introduction of term "High-Level Assembler"

#### Keywords:

Cray Supercomputing, Vectorization, Zero-Overhead-Loop-Control (ZOLC), True-Scalable Vectors, Multi-Issue Out-of-Order, Sequential Programming Model, Digital Signal Processing (DSP), High-level Assembler

#### Motivation

Just at the time when customers are asking for higher performance, the seductive lure of SIMD, as outlined in the sigarch "SIMD Considered Harmful" article, is getting out of control and damaging the reputation of mainstream general-purpose ISAs that offer it. A solution from 50 years ago exists in the form of Cray-Style True-Scalable Vectors. However the usual way that True-Scalable Vector ISAs are done *also* adds more instructions and complexifies the ISA. Simple-V takes a step back to a simpler era in computing from half a century ago: the Zilog Z80 CPIR and LDIR instructions, and the 8086 REP instruction, and brings them forward to Modernday Computing. The result is a huge reduction in programming complexity, and a strong base to project the Power ISA back to the world's most powerful Supercomputing ISA for at least the next two decades.

#### Notes and Observations:

Related RFCs are {RFC ls008} for the two Management instructions setvl and svstep, and {RFC ls009} for the REMAP Subsystem. Also {RFC ls001} is a Dependency as it introduces Primary Opcode 9 64-bit encoding. An additional RFC {RFC ls005.xlen} introduced XLEN on which SVP64 is also critically dependent, for Element-width Overrides.

#### Changes

Add the following entries to:

- A new "Vector Looping" Book

- New Vector-Looping Chapters

- New Vector-Looping Appendices

[[!tag opf\_rfc]]

# SVP64 Zero-Overhead Loop Prefix Subsystem </>

This document describes {Scalable Vectors for Power ISA} augmentation of the Power v3.0B ISA.

Credits and acknowledgements:

- Luke Leighton

- Jacob Lifshay

- Hendrik Boom

- Richard Wilbur

- Alexandre Oliva

- Cesar Strauss

- NLnet Foundation, for funding

- OpenPOWER Foundation

- Paul Mackerras

- Brad Frey

- Cathy May

- Toshaan Bharvani

- IBM for the Power ISA itself

# Introduction </>

Simple-V is a type of Vectorization best described as a "Prefix Loop Subsystem" similar to the 5 decades-old Zilog Z80  $LDIR^1$  instruction and to the 8086  $REP^2$  Prefix instruction. More advanced features are similar to the Z80  $CPIR^3$  instruction.

Except where explicitly stated all bit numbers remain as in the rest of the Power ISA: in MSB0 form (the bits are numbered from 0 at the MSB on the left and counting up as you move rightwards to the LSB end). All bit ranges are inclusive (so 4:6 means bits 4, 5, and 6, in MSB0 order). All register numbering and element numbering however is LSB0 ordering which is a different convention from that used elsewhere in the Power ISA.

The SVP64 prefix always comes before the suffix in PC order and must be considered an independent "Defined Word-instruction"<sup>4</sup> that augments the behaviour of the following instruction (also a Defined Word-instruction), but does **not** change the actual Decoding of that following instruction just because it is Prefixed. Unlike EXT100-163, where the Suffix is considered an entirely new Opcode Space, SVP64-Prefixed instructions must never be treated or regarded as a different Opcode Space.

Two apparent exceptions to the above hard rule exist: SV Branch-Conditional operations and LD/ST-update "Post-Increment" Mode. Post-Increment was considered sufficiently high priority (significantly reducing hotloop instruction count) that one bit in the Prefix is reserved for it (*Note the intention to release that bit and move Post-Increment instructions to EXT2xx, as part of* [[sv/rfc/ls011]]). Vectorized Branch-Conditional operations "embed" the original Scalar Branch-Conditional behaviour into a much more advanced variant that is highly suited to High-Performance Computation (HPC), Supercomputing, and parallel GPU Workloads.

Architectural Resource Allocation note: at present it is possible to perform partial parallel decode of the SVP64 24-bit Encoding Area at the same time as decoding of the Suffix. Multi-Issue Implementations may even Decode multiple 32-bit words in parallel and follow up with a second cycle of joining Prefix and Suffix "after-the-fact". Mixing and overlaying 64-bit Opcode Encodings into the {SVP64 24-bit Prefix}{Defined Word-instruction} space creates a hard dependency that catastrophically damages Multi-Issue Decoding by greatly complexifying Parallel Instruction-Length Detection. Therefore it has to be prohibited to accept RFCs which fundamentally violate the following hard requirement: **under no circumstances** must the use of SVP64 24-bit Suffixes **also** imply a different Opcode space from **any** non-prefixed Word. Even RESERVED or Illegal Words must be Orthogonal.

Subset implementations in hardware are permitted, as long as certain rules are followed, allowing for full soft-emulation including future revisions. Compliancy Subsets exist to ensure minimum levels of binary interoperability expectations within certain environments. Details in the {SVP64 Appendix}.

# SVP64 encoding features </>

A number of features need to be compacted into a very small space of only 24 bits:

- Independent per-register Scalar/Vector tagging and range extension on every register

- Element width overrides on both source and destination

- Predication on both source and destination

- Two different sources of predication: INT and CR Fields

- SV Modes including saturation (for Audio, Video and DSP), mapreduce, and fail-first mode.

Different classes of operations require different formats. The earlier sections cover the common formats and the five separate modes have their own section later:

• CR operations (crops),

- <sup>1</sup>Zilog Z80 LDIR

- <sup>2</sup>8086 REP

<sup>&</sup>lt;sup>3</sup>Zilog Z80 CPIR

<sup>&</sup>lt;sup>4</sup>Defined Word-instruction: Power ISA v3.1 Section 1.6

- Arithmetic/Logical (termed "normal"),

- Load/Store Immediate,

- Load/Store Indexed,

- Branch-Conditional.

# **Definition of "PO9-Prefixed" </>**

Used in the context of "A PO9-Prefixed Word" this is a new area similar to EXT100-163 that is shared between SVP64-Single, SVP64, 32 Vectorizable new Opcode areas EXT232-263, and a 32-bit area, EXT900, that is also Vectorizable and SVP64-Single extensible in future. See [[sv/po9\_encoding]].

# **Definition of "SVP64-Prefix" </>**

A 24-bit RISC-Paradigm Encoding area for Loop-Augmentation of the next "Defined Word-instructioninstruction". Used in the context of "An SVP64-Prefixed Defined Word-instruction", as separate and distinct from the 32-bit PO9-Prefix that *holds* a 24-bit SVP64 Prefix.

# Definition of "Vectorizable" and "Unvectorizable" </>

"Vectorizable" Defined Word-instructions are Scalar instructions that benefit from SVP64 Loop-Prefixing. Conversely, any operation that inherently makes no sense if repeated in a Vector Loop is termed "Unvectorizable" or "Unvectorized". Examples include sc or sync which have no registers. mtmsr is also classed as Unvectorizable because there is only one MSR.

Unvectorized instructions are required to be detected as such if Prefixed (either SVP64 or SVP64Single) and an Illegal Instruction Trap raised.

Architectural Note: Given that a "pre-classification" Decode Phase is required (identifying whether the Suffix - Defined Word-instruction - is Arithmetic/Logical, CR-op, Load/Store or Branch-Conditional), adding "Unvectorized" to this phase is not unreasonable.

Vectorizable Defined Word-instructions are **required** to be Vectorized, or they may not be permitted to be added at all to the Power ISA as Defined Word-instructions.

Engineering note: implementations may not choose to add Defined Word-instructions without also adding hardware support for SVP64-Prefixing of the same.

ISA Working Group note: Vectorized PackedSIMD instructions if ever proposed should be considered Unvectorizable and except in extreme mitigating circumstances rejected immediately.

# **Definition of Strict Element-Level Execution Order </>**

Where Instruction Execution Order<sup>5</sup> guarantees the appearance of sequential execution of instructions, Simple-V requires a corresponding guarantee for Elements because in Simple-V "Execution of Elements" is synonymous with "Execution of instructions".

# Precise Interrupt Guarantees </>

Strict Instruction Execution Order is defined as giving the appearance, as far as programs are concerned, that instructions were executed strictly in the sequence that they occurred. A "Precise" out-of-order Microarchitecture goes to considerable lengths to ensure that this is the case.

Many Vector ISAs allow interrupts to occur in the middle of processing of large Vector operations, only under the condition that partial results are cleanly discarded, and continuation on return from the Trap Handler will restart the entire operation. The reason is that saving of full Architectural State is not practical. An example would be a Floating-Point Horizontal Sum instruction (very common in Vector ISAs) or a Dot Product instruction that specifies a higher degree of accuracy for the *internal* accumulator than the registers.

Simple-V operates on an entirely different paradigm from traditional Vector ISAs: as a "Sub-Execution Context", where "Elements" are synonymous with Scalar instructions. With this in mind implementations must observe Strict **Element**-Level Execution Order[[#svp64\_eeo]] at all times. *Any* element is Interruptible, and Architectural State may be fully preserved and restored regardless of that same State.

Engineering note: implementations are permitted have higher latency to perform context-switching (particularly if REMAP is active).

Interrupts still only save MSR and PC in SRR0 and SRR1 but the full SVP64 Architectural State may be saved and restored through manual copying of SVSTATE (and the four REMAP SPRs if in use at the time, which may be determined by SVSTATE[32:46] being non-zero).

Programmer's note: Trap Handlers (and any stack-based context save/restore) must avoid the use of SVP64 Prefixed instructions to perform the necessary save/restore of Simple-V Architectural State (SPR SVSTATE), just as use of FPRs and VSRs is presently avoided. However once saved, and set to known-good, SVP64 Prefixed instructions may be used to save/restore GPRs, SPRs, FPRs and other state.

$<sup>^5</sup> Strict$  Instruction Execution Order is defined in Public v3.1 Book I Section 2.2

Programmer's note: SVSHAPE0-3 alters Element Execution Order, but only if activated in SVSHAPE. It is therefore technically possible in a Trap Handler to save SVSTATE (mfspr t0, SVSTATE), then clear bits 32-46. At this point it becomes safe to use SVP64 to save sequential batches of SPRs (setvli MAXVL=VL=4; sv.mfspr \*t0, \*SVSHAPE0)

The only major caveat for REMAP is that after an explicit change to Architectural State caused by writing to the Simple-V SPRs, some implementations may find it easier to take longer to calculate where in a given Schedule the re-mapping Indices were. Obvious examples include Interrupts occuring in the middle of a non-RADIX2 Matrix Multiply Schedule (5x3 by 3x3 for example), which will force some implementations to perform divide and modulo calculations.

An additional caveat involves Condition Register Fields when also used as Predicate Masks. An operation that overwrites the same CR Fields that are simultaneously being used as a Predicate Mask should exercise extreme care if the overwritten CR field element was needed by a subsequent Element for its Predicate Mask bit.

Some implementations may deploy Cray's technique of "Vector Chaining" (including in this case reading the CR field containing the Predicate bit until the very last moment), and consequently avoiding the risk of overwrite is the responsibility of the Programmer. hphint may be used here to good effect. Extra Special care is particularly needed here when using REMAP and also Vertical-First Mode.

The simplest option is to use Integer Predicate Masks but the caveats are stricter:

- In Vertical-First loops Programmers **must not** write to any Integers (r3, r0, r31) used as Predicate Masks. Doing so is UNDEFINED behaviour.

- An entire Vector is held up on Horizontal-First Mode if the Integer Predicate is still in in-flight Reservation Stations or pipelines. Speculative Vector Chained Execution mitigates delays but can be heavy on Reservation Station resources.

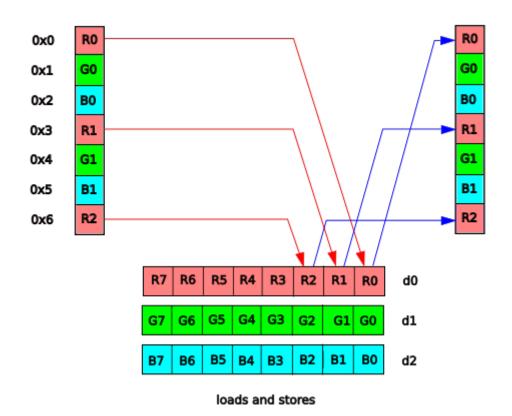

### **Register files, elements, and Element-width Overrides </>**

The relationship between register files, elements, and element-width overrides is expressed as follows:

- register files are considered to be byte-level contiguous SRAMs, accessed exclusively in Little-Endian Byte-Order at all times

- elements are sequential contiguous unbounded arrays starting at the "address" of any given 64-bit GPR or FPR, numbered from 0 as the first, "spilling" into numerically-sequentially-increasing GPRs element-width overrides set the width of the *elements* in the sequentially-numbered contiguous array.

The relationship is best defined in Canonical form, below, in ANSI c as a union data structure. A key difference is that VSR elements are bounded fixed at 128-bit, where SVP64 elements are conceptually unbounded and only limited by the Maximum Vector Length.

Future specification note: SVP64 may be defined on top of VSRs in future. At which point VSX also gains conceptually unbounded VSR register elements

In the Upper Compliancy Levels of SVP64 the size of the GPR and FPR Register files are expanded from 32 to 128 entries, and the number of CR Fields expanded from CR0-CR7 to CR0-CR127. (Note: A future version of SVP64 is anticipated to extend the VSR register file).

Memory access remains exactly the same: the effects of MSR.LE remain exactly the same, affecting as they already do and remain **only** on the Load and Store memory-register operation byte-order, and having nothing to do with the ordering of the contents of register files or register-register arithmetic or logical operations.

The only major impact on Arithmetic and Logical operations is that all Scalar operations are defined, where practical and workable, to have three new widths: elwidth=32, elwidth=16, elwidth=8.

Architectural note: a future revision of SVP64 for VSX may have entirely different definitions of possible elwidths.

The default of elwidth=64 is the pre-existing (Scalar) behaviour which remains 100% unchanged. Thus, addi is now joined by a 32-bit, 16-bit, and 8-bit variant of addi, but the sole exclusive difference is the width. In no way is the actual addi instruction fundamentally altered to become an entirely different operation (such as a subtract or multiply). FP Operations elwidth overrides are also defined, as explained in the {SVP64 Appendix}.

To be absolutely clear:

There are no conceptual arithmetic ordering or other changes over the Scalar Power ISA definitions to registers or register files or to arithmetic or Logical Operations, beyond element-width subdivision

Element offset numbering is naturally LSB0-sequentially-incrementing from zero, not MSB0incrementing including when element-width overrides are used, at which point the elements progress through each register sequentially from the LSB end (confusingly numbered the highest in MSB0 ordering) and progress incrementally to the MSB end (confusingly numbered the lowest in MSB0 ordering).

When exclusively using MSB0-numbering, SVP64 becomes unnecessarily complex to both express and subsequently understand: the required conditional subtractions from 63, 31, 15 and 7 needed to express the fact that elements are LSB0-sequential unfortunately become a hostile minefield, obscuring both intent and meaning. Therefore for the purposes of this section the more natural **LSB0 numbering is assumed** and it is left to the reader to translate to MSB0 numbering.

The Canonical specification for how element-sequential numbering and element-width overrides is defined is expressed in the following c structure, assuming a Little-Endian system, and naturally using LSB0 numbering everywhere because the ANSI c specification is inherently LSB0. Note the deliberate similarity to how VSX register elements are defined, from Figure 97, Book I, Section 6.3, Page 258:

```

#pragma pack

typedef union {

uint8_t actual_bytes[8];

// all of these are very deliberately unbounded arrays

// that intentionally "wrap" into subsequent actual_bytes...

uint8_t bytes[]; // elwidth 8

uint16_t hwords[]; // elwidth 16

uint32_t words[]; // elwidth 32

uint64_t dwords[]; // elwidth 64

} el reg t;

// ... here, as packed statically-defined GPRs.

elreg_t int_regfile[128];

// use element 0 as the destination

void get register element(el reg t* el, int gpr, int element, int width) {

switch (width) {

case 64: el->dwords[0] = int_regfile[gpr].dwords[element];

case 32: el->words[0] = int_regfile[gpr].words[element];

case 16: el->hwords[0] = int_regfile[gpr].hwords[element];

case 8 : el->bytes[0] = int_regfile[gpr].bytes[element];

}

}

// use element 0 as the source

void set_register_element(el_reg_t* el, int gpr, int element, int width) {

switch (width) {

case 64: int_regfile[gpr].dwords[element] = el->dwords[0];

case 32: int_regfile[gpr].words[element] = el->words[0];

case 16: int regfile[gpr].hwords[element] = el->hwords[0];

case 8 : int_regfile[gpr].bytes[element] = el->bytes[0];

}

}

```

Example Vector-looped add operation implementation when elwidths are 64-bit:

# vector-add RT, RA,RB using the "uint64\_t" union member, "dwords"

for i in range(VL):

int\_regfile[RT].dword[i] = int\_regfile[RA].dword[i] + int\_regfile[RB].dword[i]

However if elwidth overrides are set to 16 for both source and destination:

# vector-add RT, RA, RB using the "uint64\_t" union member "hwords"

for i in range(VL):

int regfile[RT].hwords[i] = int regfile[RA].hwords[i] + int regfile[RB].hwords[i]

The most fundamental aspect here to understand is that the wrapping into subsequent Scalar GPRs that occurs on larger-numbered elements including and especially on smaller element widths is **deliberate and intentional**. From this Canonical definition it should be clear that sequential elements begin at the LSB end of any given underlying Scalar GPR, progress to the MSB end, and then to the LSB end of the *next numerically-larger Scalar GPR*. In the example above if VL=5 and RT=1 then the contents of GPR(1) and GPR(2) will be as follows. For clarity in the table below:

• Both MSB0-ordered bitnumbering and LSB-ordered bitnumbering are shown

- The GPR-numbering is considered LSB0-ordered

- The Element-numbering (result0-result4) is LSB0-ordered

- Each of the results (result0-result4) are 16-bit

- "same" indicates "no change as a result of the Vectorized add"

| MSB0:<br>  LSB0: | 0:15<br>63:48 | 16:31<br>47:32 | 32:47<br>31:16 | 48:63  <br>15:0 |

|------------------|---------------|----------------|----------------|-----------------|

|                  |               |                |                |                 |

| GPR(0)           | same          | same           | same           | same            |

| GPR(1)           | result3       | result2        | result1        | result0         |

| GPR(2)           | same          | same           | same           | result4         |

| GPR(3)           | same          | same           | same           | same            |

|                  |               |                |                |                 |

|                  |               |                |                |                 |

Note that the upper 48 bits of GPR(2) would **not** be modified due to the example having VL=5. Thus on "wrapping" - sequential progression from GPR(1) into GPR(2) - the 5th result modifies **only** the bottom 16 LSBs of GPR(1).

If the 16-bit operation were to be followed up with a 32-bit Vectorized Operation, the exact same contents would be viewed as follows:

| MSB0:  | 0:31                 | 32:63                |

|--------|----------------------|----------------------|

| LSB0:  | 63:32                | 31:0                 |

| GPR(0) | same                 | same                 |

| GPR(1) | (result3    result2) | (result1    result0) |

| GPR(2) | same                 | (same    result4)    |

| GPR(3) | same                 | same                 |

|        | <br>                 | <br>                 |

In other words, this perspective really is no different from the situation where the actual Register File is treated as an Industry-standard byte-level-addressable Little-Endian-addressed SRAM. Note that this perspective does **not** involve MSR.LE in any way shape or form because MSR.LE is directly in control of the Memory-to-Register byte-ordering. This section is exclusively about how to correctly perceive Simple-V-Augmented **Register** Files.

Engineering note: to avoid a Read-Modify-Write at the register file it is strongly recommended to implement byte-level write-enable lines exactly as has been implemented in DRAM ICs for many decades. Additionally the predicate mask bit is advised to be associated with the element operation and alongside the result ultimately passed to the register file. When element-width is set to 64-bit the relevant predicate mask bit may be repeated eight times and pull all eight write-port byte-level lines HIGH. Clearly when element-width is set to 8-bit the relevant predicate mask bit corresponds directly with one single byte-level write-enable line. It is up to the Hardware Architect to then amortise (merge) elements together into both PredicatedSIMD Pipelines as well as simultaneous non-overlapping Register File writes, to achieve High Performance designs. Overall it helps to think of the GPR and FPR register files as being much more akin to a 64-bit-wide byte-level-addressable SRAM.

#### Comparative equivalent using VSR registers

For a comparative data point the VSR Registers may be expressed in the same fashion. The c code below is directly an expression of Figure 97 in Power ISA Public v3.1 Book I Section 6.3 page 258, after compensating for MSB0 numbering in both bits and elements, adapting in full to LSB0 numbering, and obeying LE ordering.

**Crucial to understanding why the subtraction from 1,3,7,15 is present is because the Power ISA numbers VSX Registers elements also in MSB0 order**. SVP64 very specifically numbers elements in **LSB0** order with the first element (numbered zero) being at the bitwise-numbered **LSB** end of the register, where VSX does the reverse: places the numerically-*highest* (last-numbered) element at the LSB end of the register.

```

#pragma pack

typedef union {

// these do NOT match their Power ISA VSX numbering directly, they are all reversed

// bytes[15] is actually VSR.byte[0] for example. if this convention is not

// followed then everything ends up in the wrong place

uint8_t bytes[16]; // elwidth 8, QTY 16 FIXED total

uint16_t hwords[8]; // elwidth 16, QTY 8 FIXED total

uint32_t words[4]; // elwidth 32, QTY 8 FIXED total

uint64_t dwords[2]; // elwidth 64, QTY 2 FIXED total

uint8_t actual_bytes[16]; // totals 128-bit

} el_reg_t;

elreg_t VSR_regfile[64];

static void check_num_elements(int elt, int width) {

switch (width) {

case 64: assert elt < 2;</pre>

case 32: assert elt < 4;

case 16: assert elt < 8;</pre>

case 8 : assert elt < 16;</pre>

}

}

void get VSR element(el reg t* el, int gpr, int elt, int width) {

check_num_elements(elt, width);

switch (width) {

case 64: el->dwords[0] = VSR_regfile[gpr].dwords[1-elt];

case 32: el->words[0] = VSR_regfile[gpr].words[3-elt];

case 16: el->hwords[0] = VSR_regfile[gpr].hwords[7-elt];

case 8 : el->bytes[0] = VSR_regfile[gpr].bytes[15-elt];

}

ŀ

void set VSR element(el reg t* el, int gpr, int elt, int width) {

check_num_elements(elt, width);

switch (width) {

case 64: VSR_regfile[gpr].dwords[1-elt] = el->dwords[0];

case 32: VSR_regfile[gpr].words[3-elt] = el->words[0];

```

```

case 16: VSR_regfile[gpr].hwords[7-elt] = el->hwords[0];

case 8 : VSR_regfile[gpr].bytes[15-elt] = el->bytes[0];

}

```

For VSR Registers one key difference is that the overlay of different element widths is clearly a *bounded static quantity*, whereas for Simple-V the elements are unrestrained and permitted to flow into *successive underlying Scalar registers*. This difference is absolutely critical to a full understanding of the entire Simple-V paradigm and why element-ordering, bit-numbering *and register numbering* are all so strictly defined.

Implementations are not permitted to violate the Canonical definition. Software will be critically relying on the wrapped (overflow) behaviour inherently implied by the unbounded variable-length c arrays.

Illustrating the exact same loop with the exact same effect as achieved by Simple-V we are first forced to create wrapper functions, to cater for the fact that VSR register elements are static bounded:

```

int calc VSR reg offs(int elt, int width) {

switch (width) {

case 64: return floor(elt / 2);

case 32: return floor(elt / 4);

case 16: return floor(elt / 8);

case 8 : return floor(elt / 16);

}

}

int calc_VSR_elt_offs(int elt, int width) {

switch (width) {

case 64: return (elt % 2);

case 32: return (elt % 4);

case 16: return (elt % 8);

case 8 : return (elt % 16);

}

}

void _set_VSR_element(el_reg_t* el, int gpr, int elt, int width) {

int new elt = calc VSR elt offs(elt, width);

int new reg = calc VSR reg offs(elt, width);

set_VSR_element(el, gpr+new_reg, new_elt, width);

ļ

```

And finally use these functions:

```

# VSX-add RT, RA, RB using the "uint64_t" union member "hwords"

for i in range(VL):

el_reg_t result, ra, rb;

_get_VSR_element(&ra, RA, i, 16);

_get_VSR_element(&rb, RB, i, 16);

result.hwords[0] = ra.hwords[0] + rb.hwords[0]; // use array 0 elements

_set_VSR_element(&result, RT, i, 16);

```

## Scalar Identity Behaviour </>

SVP64 is designed so that when the prefix is all zeros, and VL=1, no effect or influence occurs (no augmentation) such that all standard Power ISA v3.0/v3.1 instructions covered by the prefix are "unaltered". This is termed scalar identity behaviour (based on the mathematical definition for "identity", as in, "identity matrix" or better "identity transformation").

Note that this is completely different from when VL=0. VL=0 turns all operations under its influence into nops (regardless of the prefix) whereas when VL=1 and the SV prefix is all zeros, the operation simply acts as if SV had not been applied at all to the instruction (an "identity transformation").

The fact that VL is dynamic and can be set to any value at runtime based on program conditions and behaviour means very specifically that scalar identity behaviour is **not** a redundant encoding. If the only means by which VL could be set was by way of static-compiled immediates then this assertion would be false. VL should not be confused with MAXVL when understanding this key aspect of SimpleV.

# **Register Naming and size </>**

As indicated above SV Registers are simply the GPR, FPR and CR register files extended linearly to larger sizes; SV Vectorization iterates sequentially through these registers (LSB0 sequential ordering from 0 to VL-1).

Where the integer regfile in standard scalar Power ISA v3.0B/v3.1B is r0 to r31, SV extends this range (in the Upper Compliancy Levels of SV) as r0 to r127. Likewise FP registers are extended to 128 (fp0 to fp127), and CR Fields are extended to 128 entries, CR0 thru CR127. In the Lower SV Compliancy Levels the quantity of registers remains the same in order to reduce implementation cost for Embedded systems.

The names of the registers therefore reflects a simple linear extension of the Power ISA v3.0B / v3.1B register naming, and in hardware this would be reflected by a linear increase in the size of the underlying SRAM used for the regfiles.

Note: when an EXTRA field (defined below) is zero, SV is deliberately designed so that the register fields are identical to as if SV was not in effect i.e. under these circumstances (EXTRA=0) the register field names RA, RB etc. are interpreted and treated as v3.0B / v3.1B scalar registers. This is part of scalar identity behaviour described above.

### **Condition Register(s)**

The Scalar Power ISA Condition Register is a 64 bit register where the top 32 MSBs (numbered 0:31 in MSB0 numbering) are not used. This convention is *preserved* in SVP64 and an additional 15 Condition Registers provided in order to store the new CR Fields, CR8-CR15, CR16-CR23 etc. sequentially. The top 32 MSBs in each new SVP64 Condition Register are *also* not used: only the bottom 32 bits (numbered 32:63 in MSB0 numbering).

Programmer's note: using sv.mfcr without element-width overrides to take into account the fact that the top 32 MSBs are zero and thus effectively doubling the number of GPR registers required to hold all 128 CR Fields would seem the only option because a source elwidth override to 32-bit would take only the bottom 16 LSBs of the Condition Register and set the top 16 LSBs to zeros. However in this case it is possible to use destination element-width overrides (for sv.mfcr. source overrides would be used on the GPR of sv.mtocrf), where upon truncation of the 64-bit Condition Register(s) occurs, throwing away the zeros and storing the remaining (valid, desired) 32-bit values sequentially into (LSB0-convention) lower-numbered and upper-numbered halves of GPRs respectively. The programmer is expected to be aware however that the full width of the entire 64-bit Condition Register is considered to be "an element". This is **not** like any other Condition-Register instructions because all other CR instructions, on closer investigation, will be observed to all be CR-bit or CR-Field related. Thus a VL of 16 must be used

### **Condition Register Fields as Predicate Masks**

Condition Register Fields perform an additional duty in Simple-V: they are used for Predicate Masks. ARM's Scalar Instruction Set calls single-bit predication "Conditional Execution", and utilises Condition Codes for exactly this purpose to solve the problem caused by Branch Speculation. In a Vector ISA context the concept of Predication is naturally extended from single-bit to multi-bit, and the (well-known) benefits become all the more critical given that parallel branches in Vector ISAs are impossible (even a Vector ISA can only have Scalar branches).

However the Scalar Power ISA does not have Conditional Execution (for which, if it had ever been considered, Condition Register bits would be a perfect natural fit). Thus, when adding Predication using CR Fields via Simple-V it becomes a somewhat disruptive addition to the Power ISA.

To ameliorate this situation, particularly for pre-existing Hardware designs implementing up to Scalar Power ISA v3.1, some rules are set that allow those pre-existing designs not to require heavy modification to their existing Scalar pipelines. These rules effectively allow Hardware Architects to add the additional CR Fields CR8 to CR127 as if they were an **entirely separate register file**.

- any instruction involving more than 1 source 1 destination where one of the operands is a Condition Register is prohibited from using registers from both the CR0-7 group and the CR8-127 group at the same time.

- any instruction involving 1 source 1 destination where either the source or the destination is a Condition Register is prohibited from setting CR0-7 as a Vector.

- prohibitions are required to be enforced by raising Illegal Instruction Traps

Examples of permitted instructions:

sv.crand \*cr8.eq, \*cr16.le, \*cr40.so # all CR8-CR127sv.mfcr cr5, \*cr40# only one source (CR40) copied to CR5sv.mfcr \*cr16, cr40# Vector-Splat CR40 onto CR16,17,18...sv.mfcr \*cr16, cr3# Vector-Splat CR3 onto CR16,17,18...

Examples of prohibited instructions:

sv.mfcr \*cr0, cr40# Vector-Splat onto CR0,1,2sv.crand cr7, cr9, cr10# crosses over between CR0-7 and CR8-127

## Future expansion. </>

With the way that EXTRA fields are defined and applied to register fields, future versions of SV may involve 256 or greater registers in some way as long as the reputation of Power ISA for full backwards binary interoperability is preserved. Backwards binary compatibility may be achieved with a PCR bit (Program Compatibility Register) or an MSR bit analogous to SF. Further discussion is out of scope for this version of SVP64.

Additionally, a future variant of SVP64 will be applied to the Scalar (Quad-precision and 128-bit) VSX instructions. Element-width overrides are an opportunity to expand a future version of the Power ISA to 256-bit, 512-bit and 1024-bit operations, as well as doubling or quadrupling the number of VSX registers to 128 or 256. Again further discussion is out of scope for this version of SVP64.

# SVP64 Remapped Encoding (RM[0:23]) </>

In the SVP64 Vector Prefix spaces, the 24 bits 8-31 are termed RM. Bits 32-37 are the Primary Opcode of the Suffix "Defined Word-instruction". 38-63 are the remainder of the Defined Word-instruction. Note that the new EXT232-263 SVP64 area it is obviously mandatory that bit 32 is required to be set to 1.

| 0-5 | 6 | 7 | 8-31 | 32-37 | 38-64 | Description                          |

|-----|---|---|------|-------|-------|--------------------------------------|

|     |   |   |      |       |       | SVP64:EXT232-263<br>SVP64:EXT000-063 |

It is important to note that unlike EXT1xx 64-bit prefixed instructions there is insufficient space in RM to provide identification of any SVP64 Fields without first partially decoding the 32-bit suffix. Similar to the "Forms" (X-Form, D-Form) the RM format is individually associated with every instruction. However this still does not adversely affect Multi-Issue Decoding because the identification of the *length* of anything in the 64-bit space has been kept brutally simple (EXT009), and further decoding of any number of 64-bit Encodings in parallel at that point is fully independent.

Extreme caution and care must be taken when extending SVP64 in future, to not create unnecessary relationships between prefix and suffix that could complicate decoding, adding latency.

# Common RM fields </>

The following fields are common to all Remapped Encodings:

| Field Name | Field bits | Description                       |

|------------|------------|-----------------------------------|

| MASKMODE   | 0          | Execution (predication) Mask Kind |

| MASK       | 1:3        | Execution Mask                    |

| SUBVL      | 8:9        | Sub-vector length                 |

The following fields are optional or encoded differently depending on context after decoding of the Scalar suffix:

| Field Name  | Field bits | Description                                   |

|-------------|------------|-----------------------------------------------|

| ELWIDTH     | 4:5        | Element Width                                 |

| ELWIDTH_SRC | 6:7        | Element Width for Source (or MASK_SRC in 2PM) |

| EXTRA       | 10:18      | Register Extra encoding                       |

| MODE        | 19:23      | changes Vector behaviour                      |

- MODE changes the behaviour of the SV operation (result saturation, mapreduce)

- SUBVL groups elements together into vec2, vec3, vec4 for use in 3D and Audio/Video DSP work

- ELWIDTH and ELWIDTH SRC overrides the instruction's destination and source operand width

- MASK (and MASK\_SRC) and MASKMODE provide predication (two types of sources: scalar INT and Vector CR).

- Bits 10 to 18 (EXTRA) are further decoded depending on the RM category for the instruction, which is determined only by decoding the Scalar 32 bit suffix.

Similar to Power ISA X-Form etc. EXTRA bits are given designations, such as RM-1P-3S1D which indicates for this example that the operation is to be single-predicated and that there are 3 source operand EXTRA tags and one destination operand tag.

Note that if ELWIDTH != ELWIDTH\_SRC this may result in reduced performance or increased latency in some implementations due to lane-crossing.

# **Mode </>**

Mode is an augmentation of SV behaviour. Different types of instructions have different needs, similar to Power ISA v3.1 64 bit prefix 8LS and MTRR formats apply to different instruction types. Modes include Reduction, Iteration, arithmetic saturation, and Fail-First. More specific details in each section and in the {SVP64 Appendix}

- For condition register operations see {Condition Register Fields Mode}

- For LD/ST Modes, see {Load/Store Mode}.

- For Branch modes, see {Branch Mode}

- For arithmetic and logical, see {Arithmetic Mode}

# ELWIDTH Encoding </>

Default behaviour is set to 0b00 so that zeros follow the convention of scalar identity behaviour. In this case it means that elwidth overrides are not applicable. Thus if a 32 bit instruction operates on 32 bit, elwidth=0b00 specifies that this behaviour is unmodified. Likewise when a processor is switched from 64 bit to 32 bit mode, elwidth=0b00 states that, again, the behaviour is not to be modified.

Only when elwidth is nonzero is the element width overridden to the explicitly required value.

### Elwidth for Integers: </>

| Value | Mnemonic  | Description                     |

|-------|-----------|---------------------------------|

| 00    | DEFAULT   | default behaviour for operation |

| 01    | ELWIDTH=w | Word: 32-bit integer            |

| 10    | ELWIDTH=h | Halfword: 16-bit integer        |

| 11    | ELWIDTH=b | Byte: 8-bit integer             |

This encoding is chosen such that the byte width may be computed as 8<<(3-ew)

### Elwidth for FP Registers: </>

| Value | Mnemonic     | Description                           |

|-------|--------------|---------------------------------------|

| 00    | DEFAULT      | default behaviour for FP operation    |

| 01    | ELWIDTH=f32  | 32-bit IEEE 754 Single floating-point |

| 10    | ELWIDTH=f16  | 16-bit IEEE 754 Half floating-point   |

| 11    | ELWIDTH=bf16 | Reserved for bf16                     |

Note: bf16 is reserved for a future implementation of SV

Note that any IEEE754 FP operation in Power ISA ending in "s" (fadds) shall perform its operation at **half** the ELWIDTH then padded back out to ELWIDTH. sv.fadds/ew=f32 shall perform an IEEE754 FP16 operation that is then "padded" to fill out to an IEEE754 FP32. When ELWIDTH=DEFAULT clearly the behaviour of sv.fadds is performed at 32-bit accuracy then padded back out to fit in IEEE754 FP64, exactly as for Scalar v3.0B "single" FP. Any FP operation ending in "s" where ELWIDTH=f16 or ELWIDTH=bf16 is reserved and must raise an illegal instruction (IEEE754 FP8 or BF8 are not defined).

### Elwidth for CRs (no meaning) </>

Element-width overrides for CR Fields has no meaning. The bits are therefore used for other purposes, or when Rc=1, the Elwidth applies to the result being tested (a GPR or FPR), but not to the Vector of CR Fields.

## **SUBVL Encoding </>**

The default for SUBVL is 1 and its encoding is 0b00 to indicate that SUBVL is effectively disabled (a SUBVL for-loop of only one element). this lines up in combination with all other "default is all zeros" behaviour.

| Value | Mnemonic | Subvec | Description            |

|-------|----------|--------|------------------------|

| 00    | SUBVL=1  | single | Sub-vector length of 1 |

| 01    | SUBVL=2  | vec2   | Sub-vector length of 2 |

| 10    | SUBVL=3  | vec3   | Sub-vector length of 3 |

| 11    | SUBVL=4  | vec4   | Sub-vector length of 4 |

The SUBVL encoding value may be thought of as an inclusive range of a sub-vector. SUBVL=2 represents a vec2, its encoding is 0b01, therefore this may be considered to be elements 0b00 to 0b01 inclusive.

Effectively, SUBVL is like a SIMD multiplier: instead of just 1 element operation issued, SUBVL element operations are issued (as an inner loop). The key difference between VL looping and SUBVL looping is that predication bits are applied per **group**, rather than by individual element.

Directly related to subvl is the pack and unpack Mode bits of SVSTATE.

# MASK/MASK\_SRC & MASKMODE Encoding </>

One bit (MASKMODE) indicates the mode: CR or Int predication. The two types may not be mixed.

Special note: to disable predication this field must be set to zero in combination with Integer Predication also being set to 0b000. this has the effect of enabling "all 1s" in the predicate mask, which is equivalent to "not having any predication at all".

MASKMODE may be set to one of 2 values:

| Value | Description                                          |

|-------|------------------------------------------------------|

| 0     | MASK/MASK_SRC are encoded using Integer Predication  |

| 1     | MASK/MASK_SRC are encoded using CR-based Predication |

Integer Twin predication has a second set of 3 bits that uses the same encoding thus allowing either the same register (r3, r10 or r31) to be used for both src and dest, or different regs (one for src, one for dest).

Likewise CR based twin predication has a second set of 3 bits, allowing a different test to be applied.

Note that it cannot necessarily be assumed that Predicate Masks (whether INT or CR) are read in full *before* the operations proceed. In practice (for CR Fields) this creates an unnecessary block on parallelism, prohibiting "Vector Chaining". Therefore, it is up to the programmer to ensure that the CR field Elements used as Predicate Masks are not overwritten by any parallel Vector Loop. Doing so results in **UNDEFINED** behaviour, according to the definition outlined in the Power ISA v3.0B Specification.

Hardware Implementations are therefore free and clear to delay reading of individual CR fields until the actual predicated element operation needs to take place, safe in the knowledge that no programmer will have issued a Vector Instruction where previous elements could have overwritten (destroyed) not-yet-executed CR-Predicated element operations. This particularly is an issue when using REMAP, as the order in which CR-Field-based Predicate Mask bits could be read on a per-element execution basis could well conflict with the order in which prior elements wrote to the very same CR Field.

Additionally Programmers should avoid using r3 r10 or r30 as destination registers when these are also used as a Predicate Mask. Doing so is again UNDEFINED behaviour.

Usually in 2P MASK\_SRC is exclusively in the EXTRA area. However for LD/ST-Indexed a different Encoding is required, designated 2PM.

### Integer Predication (MASKMODE=0) </>

When the predicate mode bit is zero the 3 bits are interpreted as below. Twin predication has an identical 3 bit field similarly encoded.

MASK and MASK\_SRC may be set to one of 8 values, to provide the following meaning:

| Value | Mnemonic | Element i enabled if:        |

|-------|----------|------------------------------|

| 000   | ALWAYS   | predicate effectively all 1s |

| 001   | 1 « R3   | i == R3                      |

| 010   | R3       | R3 & (1 << i) is non-zero    |

| 011   | ~R3      | R3 & (1 << i) is zero        |

| 100   | R10      | R10 & (1 << i) is non-zero   |

| 101   | ~R10     | R10 & (1 << i) is zero       |

| 110   | R30      | R30 & (1 << i) is non-zero   |

| 111   | ~R30     | R30 & (1 << i) is zero       |

r10 and r30 are at the high end of temporary and unused registers, so as not to interfere with register allocation from ABIs.

### CR-based Predication (MASKMODE=1) </>

When the predicate mode bit is one the 3 bits are interpreted as below. Twin predication has an identical 3 bit field similarly encoded.

MASK and MASK\_SRC may be set to one of 8 values, to provide the following meaning:

| Value                                         | Mnemonic                                        | Element i is enabled if                                                                                                                                                    |

|-----------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000<br>001<br>010<br>011<br>100<br>101<br>110 | lt<br>nl/ge<br>gt<br>ng/le<br>eq<br>ne<br>so/un | CR[offs+i].LT is set<br>CR[offs+i].LT is clear<br>CR[offs+i].GT is set<br>CR[offs+i].GT is clear<br>CR[offs+i].EQ is set<br>CR[offs+i].EQ is clear<br>CR[offs+i].FU is set |

| 111                                           | ns/nu                                           | CR[offs+i].FU is clear                                                                                                                                                     |

offs is defined as CR32 (4x8) so as to mesh cleanly with Vectorized Rc=1 operations (see below). Rc=1 operations start from CR8 (TBD).

The CR Predicates chosen must start on a boundary that Vectorized CR operations can access cleanly, in full. With EXTRA2 restricting starting points to multiples of 8 (CR0, CR8, CR16...) both Vectorized Rc=1 and CR Predicate Masks have to be adapted to fit on these boundaries as well.

### Extra Remapped Encoding </>

Shows all instruction-specific fields in the Remapped Encoding RM[10:18] for all instruction variants. Note that due to the very tight space, the encoding mode is *not* included in the prefix itself. The mode is "applied", similar to Power ISA "Forms" (X-Form, D-Form) on a per-instruction basis, and, like "Forms" are given a des-

ignation (below) of the form RM-nP-nSnD. The full list of which instructions use which remaps is here {SVP64 Augmentation Table}.

#### Please note the following:

Machine-readable CSV files have been autogenerated which will make the task of creating SV-aware ISA decoders, documentation, assembler tools compiler tools Simulators documentation all aspects of SVP64 easier and less prone to mistakes. Please avoid manual re-creation of information from the written specification wording in this chapter, and use the CSV files or use the Canonical tool which creates the CSV files, named sv\_analysis.py. The information contained within sv\_analysis.py is considered to be part of this Specification, even encoded as it is in python3.

The mappings are part of the SVP64 Specification in exactly the same way as X-Form, D-Form. New Scalar instructions added to the Power ISA will need a corresponding SVP64 Mapping, which can be derived by-rote from examining the Register "Profile" of the instruction.

There are two categories: Single and Twin Predication. Due to space considerations further subdivision of Single Predication is based on whether the number of src operands is 2 or 3. With only 9 bits available some compromises have to be made.

- RM-1P-3S1D Single Predication dest/src1/2/3, applies to 4-operand instructions (fmadd, isel, madd).

- RM-1P-2S1D Single Predication dest/src1/2 applies to 3-operand instructions (src1 src2 dest)

- RM-2P-1S1D Twin Predication (src=1, dest=1)

- RM-2P-2S1D Twin Predication (src=2, dest=1) primarily for LDST (Indexed)

- RM-2P-1S2D Twin Predication (src=1, dest=2) primarily for LDST Update

- RM-2PM-2S1D Twin Predication (src=2, dest=1) for LD/ST Update (Indexed)

The 2PM designation uses bits 6 and 7 as well as the 9 EXTRA bits in order to extend two registers to EXTRA3, sacrificing destination elwidths in the process. MASK\_SRC has a different encoding in 2PM.

#### RM-1P-3S1D </>

| Field Name   | Field bits | Description                          |

|--------------|------------|--------------------------------------|

| Rdest_EXTRA2 | 10:11      | extends Rdest (R*_EXTRA2 Encoding)   |

| Rsrc1_EXTRA2 | 12:13      | extends Rsrc1 (R*_EXTRA2 Encoding)   |

| Rsrc2_EXTRA2 | 14:15      | extends Rsrc2 (R*_EXTRA2 Encoding)   |

| Rsrc3_EXTRA2 | 16:17      | extends Rsrc3 (R*_EXTRA2 Encoding)   |

| EXTRA2_MODE  | 18         | used by divmod2du and maddedu for RS |

These are for 3 operand in and either 1 or 2 out instructions. 3-in 1-out includes madd RT,RA,RB,RC. (DRAFT) instructions such as maddedu have an implicit second destination, RS, the selection of which is determined by bit 18.

### RM-1P-2S1D </>

| Field Name   | Field bits | Description   |  |

|--------------|------------|---------------|--|

| Rdest_EXTRA3 | 10:12      | extends Rdest |  |

| Rsrc1_EXTRA3 | 13:15      | extends Rsrc1 |  |

| Rsrc2_EXTRA3 | 16:18      | extends Rsrc3 |  |

These are for 2 operand 1 dest instructions, such as add RT, RA, RB. However also included are unusual instructions with an implicit dest that is identical to its src reg, such as rlwinmi.

Normally, with instructions such as rlwinmi, the scalar v3.0B ISA would not have sufficient bit fields to allow an alternative destination. With SV however this becomes possible. Therefore, the fact that the dest is implicitly also a src should not mislead: due to the *prefix* they are different SV regs.

- rlwimi RA, RS, ...

- Rsrc1\_EXTRA3 applies to RS as the first src

- Rsrc2\_EXTRA3 applies to RA as the second src

- Rdest\_EXTRA3 applies to RA to create an **independent** dest.

With the addition of the EXTRA bits, the three registers each may be *independently* made vector or scalar, and be independently augmented to 7 bits in length.

#### RM-2P-1S1D/2S </>

| Field Name   | Field bits | Description   |  |

|--------------|------------|---------------|--|

| Rdest_EXTRA3 | 10:12      | extends Rdest |  |

| Field Name Field bits |       | Description               |  |  |

|-----------------------|-------|---------------------------|--|--|

| Rsrc1_EXTRA3          | 13:15 | extends Rsrc1             |  |  |

| MASK_SRC              | 16:18 | Execution Mask for Source |  |  |

RM-2P-2S is for stw etc. and is Rsrc1 Rsrc2.

| Field Name Field bits |       | Description               |  |  |

|-----------------------|-------|---------------------------|--|--|

| Rsrc1_EXTRA3          | 10:12 | extends Rsrc1             |  |  |

| Rsrc2_EXTRA3          | 13:15 | extends Rsrc2             |  |  |

| MASK_SRC              | 16:18 | Execution Mask for Source |  |  |

### RM-1P-2S1D </>

single-predicate, three registers (2 read, 1 write)

| Field Name   | Field bits | Description   |  |

|--------------|------------|---------------|--|

| Rdest_EXTRA3 | 10:12      | extends Rdest |  |

| Rsrc1_EXTRA3 | 13:15      | extends Rsrc1 |  |

| Rsrc2_EXTRA3 | 16:18      | extends Rsrc2 |  |

#### RM-2P-2S1D/1S2D/3S </>

The primary purpose for this encoding is for Twin Predication on LOAD and STORE operations. see {Load/Store Mode} for detailed analysis.

### RM-2P-2S1D:

| Field Name   | Field bits | Description                        |

|--------------|------------|------------------------------------|

| Rdest_EXTRA2 | 10:11      | extends Rdest (R*_EXTRA2 Encoding) |

| Rsrc1_EXTRA2 | 12:13      | extends Rsrc1 (R*_EXTRA2 Encoding) |

| Rsrc2_EXTRA2 | 14:15      | extends Rsrc2 (R*_EXTRA2 Encoding) |

| MASK_SRC     | 16:18      | Execution Mask for Source          |

#### **RM-2P-1S2D**:

For RM-2P-1S2D dest2 is in bits 14:15

| Field Name    | Field bits | Description                          |

|---------------|------------|--------------------------------------|

| Rdest_EXTRA2  | 10:11      | extends Rdest (R*_EXTRA2 Encoding)   |

| Rsrc1_EXTRA2  | 12:13      | extends Rsrc1 (R*_EXTRA2 Encoding)   |

| Rdest2_EXTRA2 | 14:15      | extends Rdest22 (R*_EXTRA2 Encoding) |

| MASK_SRC      | 16:18      | Execution Mask for Source            |

#### **RM-2P-3S:**

Also that for RM-2P-3S (to cover stdx etc.) the names are switched to 3 src: Rsrc1\_EXTRA2, Rsrc2\_EXTRA2, Rsrc3\_EXTRA2.

| Field Name                                               | Field bits | Description                                                                                                                                 |

|----------------------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Rsrc1_EXTRA2<br>Rsrc2_EXTRA2<br>Rsrc3_EXTRA2<br>MASK_SRC |            | extends Rsrc1 (R*_EXTRA2 Encoding)<br>extends Rsrc2 (R*_EXTRA2 Encoding)<br>extends Rsrc3 (R*_EXTRA2 Encoding)<br>Execution Mask for Source |

Note also that LD with update indexed, which takes 2 src and creates 2 dest registers (e.g. lhaux RT,RA,RB), does not have room for 4 registers and also Twin Predication. Therefore these are treated as RM-2P-2S1D and the src spec for RA is also used for the same RA as a dest.

Note that if ELWIDTH != ELWIDTH\_SRC this may result in reduced performance or increased latency in some implementations due to lane-crossing.

#### RM-2PM-2S1D/1S2D/3S </>

The primary purpose for this encoding is for Twin Predication on LOAD and STORE operations providing EXTRA3 for RT, RA and RS. see {Load/Store Mode} for detailed analysis.

#### RM-2PM-2S1D:

RT or RS requires EXTRA3, RA requires EXTRA3, but for RB EXTRA2 will suffice. MASK\_SRC may be read from the bits normally used for dest-elwidth.

| Field Name   | Field bits | Description                        |

|--------------|------------|------------------------------------|

| Rdest_EXTRA3 | 10:12      | extends Rdest (R*_EXTRA2 Encoding) |

| Rsrc1_EXTRA3 | 13:15      | extends Rsrc1 (R*_EXTRA2 Encoding) |

| Rsrc2_EXTRA2 | 16:17      | extends Rsrc2 (R*_EXTRA2 Encoding) |

| MASK_SRC     | 6:7,18     | Execution Mask for Source          |

### R\*\_EXTRA2/3 </>

EXTRA is the means by which two things are achieved:

- 1. Registers are marked as either Vector *or Scalar*

- 2. Register field numbers (limited typically to 5 bit) are extended in range, both for Scalar and Vector.

The register files are therefore extended:

- INT (GPR) is extended from r0-31 to r0-127

- FP (FPR) is extended from fp0-32 to fp0-fp127

- CR Fields are extended from CR0-7 to CR0-127

However due to pressure in RM.EXTRA not all these registers are accessible by all instructions, particularly those with a large number of operands (madd, isel).

In the following tables register numbers are constructed from the standard v3.0B / v3.1B 32 bit register field (RA, FRA) and the EXTRA2 or EXTRA3 field from the SV Prefix, determined by the specific RM-xx-yyyy designation for a given instruction. The prefixing is arranged so that interoperability between prefixing and nonprefixing of scalar registers is direct and convenient (when the EXTRA field is all zeros).

A pseudocode algorithm explains the relationship, for INT/FP (see {SVP64 Appendix} for CRs)

Future versions may extend to 256 by shifting Vector numbering up. Scalar will not be altered.

Note that in some cases the range of starting points for Vectors is limited.

#### INT/FP EXTRA3 </>

If EXTRA3 is zero, maps to "scalar identity" (scalar Power ISA field naming).

Fields are as follows:

- Value: R\_EXTRA3

- Mode: register is tagged as scalar or vector

- Range/Inc: the range of registers accessible from this EXTRA encoding, and the "increment" (accessibil-

- ity). "/4" means that this EXTRA encoding may only give access (starting point) every 4th register.

- MSB..LSB: the bit field showing how the register opcode field combines with EXTRA to give (extend) the register number (GPR)

Encoding shown in LSB0: MSB down to LSB (MSB 6..0 LSB)

| Value | Mode   | Range/Inc  | 60      |

|-------|--------|------------|---------|

| 000   | Scalar | r0-r31/1   | 0b00 RA |

| 001   | Scalar | r32-r63/1  | 0b01 RA |

| 010   | Scalar | r64-r95/1  | 0b10 RA |

| 011   | Scalar | r96-r127/1 | 0b11 RA |

| 100   | Vector | r0-r124/4  | RA 0b00 |

| 101   | Vector | r1-r125/4  | RA 0b01 |

| 110   | Vector | r2-r126/4  | RA 0b10 |

| 111   | Vector | r3-r127/4  | RA 0b11 |

### INT/FP EXTRA2 </>

If EXTRA2 is zero will map to "scalar identity behaviour" i.e Scalar Power ISA register naming: Encoding shown in LSB0: MSB down to LSB (MSB 6..0 LSB)

| Value | Mode   | Range/inc | 60      |

|-------|--------|-----------|---------|

| 00    | Scalar | r0-r31/1  | 0b00 RA |

| 01    | Scalar | r32-r63/1 | 0b01 RA |

| 10    | Vector | r0-r124/4 | RA 0b00 |

| 11    | Vector | r2-r126/4 | RA 0b10 |

#### Note that unlike in EXTRA3, in EXTRA2:

- the GPR Vectors may only start from r0, r2, r4, r6, r8 and likewise FPR Vectors.

- the GPR Scalars may only go from r0, r1, r2.. r63 and likewise FPR Scalars.

as there is insufficient bits to cover the full range.

#### CR Field EXTRA3 </>

CR Field encoding is essentially the same but made more complex due to CRs being bit-based, because the application of SVP64 element-numbering applies to the CR *Field* numbering not the CR register *bit* numbering. Note that Vectors may only start from CR0, CR4, CR8, CR12, CR16, CR20... and Scalars may only go from CR0, CR1, ... CR31

Encoding shown in LSB0: MSB down to LSB (MSB 8..5 4..2 1..0 LSB), BA ranges are in MSB0.

For a 5-bit operand (BA, BB, BT):

| Value | Mode   | Range/Inc     | 85        | 42      | 10      |

|-------|--------|---------------|-----------|---------|---------|

| 000   | Scalar | CR0-CR7/1     | 0b0000    | BA[0:2] | BA[3:4] |

| 001   | Scalar | CR8-CR15/1    | 0b0001    | BA[0:2] | BA[3:4] |

| 010   | Scalar | CR16-CR23/1   | 0b0010    | BA[0:2] | BA[3:4] |

| 011   | Scalar | CR24-CR31/1   | 0b0011    | BA[0:2] | BA[3:4] |

| 100   | Vector | CR0-CR112/16  | BA[0:2] 0 | 0b000   | BA[3:4] |

| 101   | Vector | CR4-CR116/16  | BA[0:2] 0 | 0b100   | BA[3:4] |

| 110   | Vector | CR8-CR120/16  | BA[0:2] 1 | 0b000   | BA[3:4] |

| 111   | Vector | CR12-CR124/16 | BA[0:2] 1 | 0b100   | BA[3:4] |

For a 3-bit operand (e.g. BFA):

| Value | Mode   | Range/Inc     | 63     | 20    |

|-------|--------|---------------|--------|-------|

| 000   | Scalar | CR0-CR7/1     | 0b0000 | BFA   |

| 001   | Scalar | CR8-CR15/1    | 0b0001 | BFA   |

| 010   | Scalar | CR16-CR23/1   | 0b0010 | BFA   |

| 011   | Scalar | CR24-CR31/1   | 0b0011 | BFA   |

| 100   | Vector | CR0-CR112/16  | BFA 0  | 0b000 |

| 101   | Vector | CR4-CR116/16  | BFA 0  | 0b100 |

| 110   | Vector | CR8-CR120/16  | BFA 1  | 0b000 |

| 111   | Vector | CR12-CR124/16 | BFA 1  | 0b100 |

#### CR EXTRA2 </>

CR encoding is essentially the same but made more complex due to CRs being bit-based, because the application of SVP64 element-numbering applies to the CR *Field* numbering not the CR register *bit* numbering. Note that Vectors may only start from CR0, CR8, CR16, CR24, CR32...

Encoding shown in LSB0: MSB down to LSB (MSB 8..5 4..2 1..0 LSB), BA ranges are in MSB0.

For a 5-bit operand (BA, BB, BC):

| Value | Mode   | Range/Inc    | 85        | 42      | 10      |

|-------|--------|--------------|-----------|---------|---------|

| 00    | Scalar | CR0-CR7/1    | 0b0000    | BA[0:2] | BA[3:4] |

| 01    | Scalar | CR8-CR15/1   | 0b0001    | BA[0:2] | BA[3:4] |

| 10    | Vector | CR0-CR112/16 | BA[0:2] 0 | 0b000   | BA[3:4] |

| 11    | Vector | CR8-CR120/16 | BA[0:2] 1 | 0b000   | BA[3:4] |

For a 3-bit operand (e.g. BFA):

| Value | Mode   | Mode Range/Inc |        | 20    |

|-------|--------|----------------|--------|-------|

| 00    | Scalar | CR0-CR7/1      | 0b0000 | BFA   |

| 01    | Scalar | CR8-CR15/1     | 0b0001 | BFA   |

| 10    | Vector | CR0-CR112/16   | BFA 0  | 0b000 |

| 11    | Vector | CR8-CR120/16   | BFA 1  | 0b000 |

# Normal SVP64 Modes, for Arithmetic and Logical Operations </>

- https://bugs.libre-soc.org/show\_bug.cgi?id=574

- https://bugs.libre-soc.org/show\_bug.cgi?id=558#c47 https://bugs.libre-soc.org/show\_bug.cgi?id=936 write on failfirst

- {SVP64 Chapter}

Normal SVP64 Mode covers Arithmetic and Logical operations to provide suitable additional behaviour. The Mode field is bits 19-23 of the {SVP64 Chapter} RM Field.

Table of contents:

[[!toc]]

### **Mode </>**

Mode is an augmentation of SV behaviour, providing additional functionality. Some of these alterations are element-based (saturation), others are Vector-based (mapreduce, fail-on-first).

{Load/Store Mode}, {Condition Register Fields Mode} and {Branch Mode} are covered separately: the following Modes apply to Arithmetic and Logical SVP64 operations:

- simple mode is straight vectorization. No augmentations: the vector comprises an array of independently created results.

- ffirst or data-dependent fail-on-first: see separate section. The vector may be truncated depending on certain criteria. VL is altered as a result.

- sat mode or saturation: clamps each element result to a min/max rather than overflows / wraps. Allows signed and unsigned clamping for both INT and FP.

- **reduce mode**. If used correctly, a mapreduce (or a prefix sum) is performed. See {SVP64 Appendix}. Note that there are comprehensive caveats when using this mode, and it should not be confused with the Parallel Reduction {REMAP subsystem}. Also care is needed with hphint.

Note that ffirst and reduce modes are not anticipated to be high-performance in some implementations. ffirst due to interactions with VL, and reduce due to it creating overlapping operations in many of its uses. simple and saturate are however inter-element independent and may easily be parallelised to give high performance, regardless of the value of VL.

The Mode table for Arithmetic and Logical operations, being bits 19-23 of SVP64 RM, is laid out as follows:

| 0-1   | 2   | 34     | description                    |

|-------|-----|--------|--------------------------------|

| 0 0   | 0   | dz sz  | simple mode                    |

| 0 0   | 1   | RG 0   | scalar reduce mode (mapreduce) |

| 0 0   | 1   | / 1    | reserved                       |

| 10    | Ν   | dz sz  | sat mode: N=0/1 u/s            |

| VLi 1 | inv | CR-bit | Rc=1: ffirst CR sel            |

| VLi 1 | inv | zz RC1 | Rc=0: ffirst z/nonz            |

|       |     |        |                                |

Fields:

- sz / dz source-zeroing, destination-zeroing. if predication is enabled will put zeros into the dest (or as src in the case of twin pred) when the predicate bit is zero. Otherwise the element is ignored or skipped, depending on context.

- **zz**: both sz and dz are set equal to this flag

- inv CR bit just as in branches (BO) these bits allow testing of a CR bit and whether it is set (inv=0) or unset (inv=1)

- **RG** inverts the Vector Loop order (VL-1 downto 0) rather than the normal 0..VL-1

- N sets signed/unsigned saturation.

- **RC1** as if Rc=1, on operations that do not have it (typically Logical)

- VLi VL inclusive: in fail-first mode, the truncation of VL includes the current element at the failure point rather than excludes it from the count.

For LD/ST Modes, see {Load/Store Mode}. For Condition Registers see {Condition Register Fields Mode}. For Branch modes, see {Branch Mode}.

## Rounding, clamp and saturate </>

See {Audio and Video Opcodes} for relevant opcodes and use-cases.

To help ensure for example that audio quality is not compromised by overflow, "saturation" is provided, as well as a way to detect when saturation occurred if desired (Rc=1). When Rc=1 there will be a vector of CRs, one CR per element in the result (Note: this is different from VSX which has a single CR per block).

When N=0 the result is saturated to within the maximum range of an unsigned value. For integer ops this will be 0 to 2^elwidth-1. Similar logic applies to FP operations, with the result being saturated to maximum rather than returning INF, and the minimum to +0.0

When N=1 the same occurs except that the result is saturated to the min or max of a signed result, and for FP to the min and max value rather than returning +/- INF.

When Rc=1, the CR "overflow" bit is set on the CR associated with the element, to indicate whether saturation occurred. Note that due to the hugely detrimental effect it has on parallel processing, XER.SO is **ignored** completely and is **not** brought into play here. The CR overflow bit is therefore simply set to zero if saturation did not occur, and to one if it did. This behaviour (ignoring XER.SO) is actually optional in the SFFS Compliancy Subset: for SVP64 it is made mandatory *but only on Vectorized instructions*.

Note also that saturate on operations that set OE=1 must raise an Illegal Instruction due to the conflicting use of the CR.so bit for storing if saturation occurred. Vectorized Integer Operations that produce a Carry-Out (CA, CA32): these two bits will be UNDEFINED if saturation is also requested.

Note that the operation takes place at the maximum bitwidth (max of src and dest elwidth) and that truncation occurs to the range of the dest elwidth.

Programmer's Note: Post-analysis of the Vector of CRs to find out if any given element hit saturation may be done using a mapreduced CR op (cror), or by using the new crrweird instruction with Rc=1, which will transfer the required CR bits to a scalar integer and update CR0, which will allow testing the scalar integer for nonzero. See {CR Weird ops}. Alternatively, a Data-Dependent Fail-First may be used to truncate the Vector Length to non-saturated elements, greatly increasing the productivity of parallelised inner hot-loops.

# Reduce mode </>

Reduction in SVP64 is similar in essence to other Vector Processing ISAs, but leverages the underlying scalar Base v3.0B operations. Thus it is more a convention that the programmer may utilise to give the appearance and effect of a Horizontal Vector Reduction. Due to the unusual decoupling it is also possible to perform prefix-sum (Fibonacci Series) in certain circumstances. Details are in the {SVP64 Appendix}

Reduce Mode should not be confused with Parallel Reduction {REMAP subsystem}. As explained in the {SVP64 Appendix} Reduce Mode switches off the check which would normally stop looping if the result register is scalar. Thus, the result scalar register, if also used as a source scalar, may be used to perform sequential accumulation. This *deliberately* sets up a chain of Register Hazard Dependencies (which advanced hardware may optimise out), whereas Parallel Reduce {REMAP subsystem} deliberately issues a Tree-Schedule of operations that may be parallelised.

Hardware architectural note: implementations may optimise out the Hazard Dependency chain as long as Sequential Program Execution Order is preserved. Easy examples include Reduction on Logical OR or AND operations.

### Horizontal Parallelism Hint

SVSTATE.hphint declares to hardware that groups of elements up to this size are 100% independent (free of all Hazards inter-element but not inter-group). With Reduction literally creating Dependency Hazards on every element-level sub-instruction it is pretty clear that setting hphint *at all* would cause data corruption. However sv.add \*r0, \*r4, \*r0 for example clearly leaves room for four parallel elements. Programmers must be aware of this and exercise caution.

## Data-dependent Fail-on-first </>

Data-dependent fail-on-first is CR-field-driven and is completely separate and distinct from LD/ST Fail-First (also known as Fault-First). Note in each case the assumption is that vector elements are required to appear to be executed in sequential Program Order. When REMAP is not active, element 0 would be the first.

Arithmetic/Logical Data-driven (CR-field-driven) fail-on-first performs a test of the result, similar to Branch-Conditional B0 field testing, and if the test fails, the Vector Loop operation terminates, and VL is truncated to either the *previous* element or the current one, depending on whether VLi (VL "inclusive") is clear or set, respectively.

Thus the new VL comprises a contiguous vector of results, all of which pass the testing criteria (equal to zero, less than zero etc as defined by the CR-bit test). When Rc=1 the Condition Regster Field for the element just tested is always written out (regardless of VLi).

- **VLi=0** Only elements that passed the test are written out. When Rc=1 the co-result CR Field element is written out (even if the current test failed). Vector length is truncated to "elements that passed"

- VLi=1 Elements that were *tested* are written out. When Rc=1 the co-result CR Field element is written out. Vector length is truncated to "elements tested up to the first fail point"

Note: when VLi is clear, the behaviour at first seems counter-intuitive. A result is calculated but if the test fails it is prohibited from being actually written. This becomes intuitive again when it is remembered that the length that VL is set to is the number of written\* elements, and only when VLI is set will the current element be included in that count.\*

The CR-based data-driven fail-on-first is "new" and not found in ARM SVE or RVV. At the same time it is "old" because it is almost identical to a generalised form of Z80's CPIR instruction. It is extremely useful for reducing instruction count, however requires speculative execution involving modifications of VL to get high performance implementations. An additional mode (RC1=1) allows instructions that would not normally have an Rc=1 mode to at least be tested for zero or non-zero. The CR is stored (and the CR.eq bit tested against the inv field). If the CR.eq bit is equal to inv then the Vector is truncated and the loop ends.

VLi is only available as an option when Rc=0 (or for instructions which do not have Rc). When set, the current element is always also included in the count (the new length that VL will be set to). This may be useful in combination with "inv" to truncate the Vector to *exclude* elements that fail a test, or, in the case of implementations of strncpy, to include the terminating zero.

In CR-based data-driven fail-on-first there is only the option to select and test one bit of each CR (just as with branch BO). For more complex tests this may be insufficient. If that is the case, a vectorized crop such as crand, cror or {CR Weird ops} crweirder may be used, and ffirst applied to the crop instead of to the arithmetic vector. Note that crops are covered by the {Condition Register Fields Mode} Mode format.

Use of Fail-on-first with Vertical-First Mode is not prohibited but is not really recommended. The effect of truncating VL may have unintended and unexpected consequences on subsequent instructions. VLi set will be fine: it is when VLi is clear that problems may be faced.

Programmer's note: VLi is only accessible in normal operations which in turn limits the CR field bit-testing to only EQ/NE. {Condition Register Fields Mode} are not so limited. Thus it is possible to use for example sv.cror/ff=gt/vli \*0,\*0,\*0, which is not a nop because it allows Fail-First Mode to perform a test and truncate VL.

Hardware implementor's note: effective Sequential Program Order must be preserved. Speculative Execution is perfectly permitted as long as the speculative elements are held back from writing to register files (kept in Resevation Stations), until such time as the relevant CR Field bit(s) has been analysed. All Speculative elements sequentially beyond the test-failure point **MUST** be cancelled. This is no different from standard Out-of-Order Execution and the modification effort to efficiently support Data-Dependent Fail-First within a pre-existing Multi-Issue Out-of-Order Engine is anticipated to be minimal. In-Order systems on the other hand are expected, unavoidably, to be low-performance unless they also make use of SVSTATE.hphint and exploit it to safely implement rudimentary Shadow-Commit-Hold normally only found in Out-of-Order systems.

Two extremely important aspects of ffirst are:

- LDST ffirst may never set VL equal to zero. This because on the first element an exception must be raised "as normal".

- CR-based data-dependent ffirst on the other hand **can** set VL equal to zero. When VL is set zero due to the first element failing the CR bit-test, all subsequent vectorized operations are effectively nops which is *precisely the desired and intended behaviour*.

The second crucial aspect, compared to LDST Ffirst:

- LD/ST Failfirst may (beyond the initial first element conditions) truncate VL for any architecturally suitable reason. Beyond the first element LD/ST Failfirst is arbitrarily speculative and 100% non-deterministic.

- CR-based data-dependent first on the other hand MUST NOT truncate VL arbitrarily to a length decided by the hardware: VL MUST only be truncated based explicitly on whether a test fails. This because it is a precise Deterministic test on which algorithms can and will rely.

#### **Floating-point Exceptions**

When Floating-point exceptions are enabled VL must be truncated at the point where the Exception appears not to have occurred. If VLi is set then VL must include the faulting element, and thus the faulting element will always raise its exception. If however VLi is clear then VL **excludes** the faulting element and thus the exception will **never** be raised.

Although very strongly discouraged the Exception Mode that permits Floating Point Exception notification to arrive too late to unwind is permitted (under protest, due it violating the otherwise 100% Deterministic nature of Data-dependent Fail-first).

Use of lax FP Exception Notification Mode could result in parallel computations proceeding with invalid results that have to be explicitly detected, whereas with the strict FP Execption Mode enabled, FFirst truncates VL, allows subsequent parallel computation to avoid the exceptions entirely

## Data-dependent fail-first on CR operations (crand etc) </>

Operations that actually produce or alter CR Field as a result have their own SVP64 Mode, described in {Condition Register Fields Mode}.

[[!tag standards]]

# SV Load and Store </>

This section describes how Standard Load/Store Defined Word-instructions are exploited as Element-level Load/Stores and augmented to create direct equivalents of Vector Load/Store instructions.

# Modes overview </>

Vectorization of Load and Store requires creation, from scalar operations, a number of different modes:

- fixed aka "unit" stride contiguous sequence with no gaps

- element strided sequential but regularly offset, with gaps

- vector indexed vector of base addresses and vector of offsets

- Speculative Fault-first where it makes sense to do so

- Data-Dependent Fail-First Conditional truncation of Vector Length

- **Structure Packing** covered in SV by {REMAP subsystem} and Pack/Unpack Mode.

Despite being constructed from Scalar LD/ST none of these Modes exist or make sense in any Scalar ISA. They **only** exist in Vector ISAs and are a critical part of its value.

Also included in SVP64 LD/ST is Element-width overrides and Twin-Predication.