Power ISA™ Version 3.1

May 1, 2020

# **IBM**®

© Copyright International Business Machines Corporation 1994 - 2020. All rights reserved.

Printed in the United States of America May, 2020

By downloading the POWER® Instruction Set Architecture ("ISA") Specification, you agree to be bound by the terms and conditions of this agreement.

IBM, the IBM logo, and ibm.com are trademarks or registered trademarks of International Business Machines Corp., registered in many jurisdictions worldwide. Other product and service names might be trademarks of IBM or other companies. A current list of IBM trademarks is available on the Web at "Copyright and trademark information" at www.ibm.com/legal/copytrade.shtml.

Other company, product, and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

**Note**: This document contains information on products in the design, sampling and/or initial production phases of development. This information is subject to change without notice. Verify with your IBM field applications engineer that you have the latest version of this document before finalizing a design.

You may use this documentation solely for developing technology products compatible with Power Architecture® in support of growing the POWER ecosystem. You may not modify this documentation. You may distribute the documentation to suppliers and other contractors hired by you solely to produce your technology products compatible with Power Architecture® technology and to your customers (either directly or indirectly through your resellers) in conjunction with their use and instruction of your technology products compatible with Power Architecture® technology. This agreement does not include rights to create a CPU design to run the POWER ISA unless such rights have been granted

by IBM under a separate agreement. The POWER ISA specification is protected by copyright and the practice or implementation of the information herein may be protected by one or more patents or pending patent applications. No other license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. IBM makes no representations or warranties, either express or implied, including but not limited to, warranties of merchantability, fitness for a particular purpose, or non-infringement, or that any practice or implementation of the IBM documentation will not infringe any third party patents, copyrights, trade secrets, or other rights. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

The IBM home page can be found at **ibm.com**®.

The following paragraph does not apply to the United Kingdom or any country or state where such provisions are inconsistent with local law.

The specifications in this manual are subject to change without notice. This manual is provided "AS IS". International Business Machines Corp. makes no warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

International Business Machines Corp. does not warrant that the contents of this publication or the accompanying source code examples, whether individually or as one or more groups, will meet your requirements or that the publication or the accompanying source code examples are error-free.

This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication.

Address comments to IBM Corporation, 11400 Burnett Road, Austin, Texas 78758-3493. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

The following terms are trademarks of the International Business Machines Corporation in the United States and/or other countries:

IBM®

Power ISA

PowerPC®

Power Architecture®

PowerPC Architecture

RISC/System 6000

POWER®

POWER2

POWER4

POWER5

POWER5

POWER7®

POWER8®

POWER8®

POWER8®

POWER8®

System/370

Notice to U.S. Government Users—Documentation Related to Restricted Rights—Use, duplication or disclosure is subject to restrictions set fourth in GSA ADP Schedule Contract with IBM Corporation.

# **Preface**

The roots of the Power ISA (Instruction Set Architecture) extend back 30 years, to IBM Research. The POWER (Performance Optimization With Enhanced RISC) Architecture was introduced with the RISC System/6000 product family in early 1990. In 1991, Apple, IBM, and Motorola began the collaboration to evolve to the PowerPC Architecture, expanding the architecture's applicability. In 1997, Motorola and IBM began another collaboration, focused on optimizing PowerPC for embedded systems, which produced Book E.

In 2006, Freescale and IBM collaborated on the creation of the Power ISA Version 2.03, which represented the reunification of the architecture by combining Book E content with the more general purpose PowerPC Version 2.02. The resulting architecture included environment-specific privileged architecture optimizations (two Book IIIs) and optional application-specific facilities (categories) as extensions to a pervasive base architecture.

In support of the OpenPOWER Foundation's standardization of server architecture, Power ISA Version 3.0 streamlined this integration by choosing a single Book III and a set of widely used categories to become part of the base architecture for all forward-looking Power implementations. All other optional architecture categories were eliminated to ensure increased application portability between Power processors. Legacy embedded applications that require the eliminated material will continue to use V. 2.07B.

- Power ISA Version 3.0C took the first step in re-introducing optionality into the architecture as the Power ISA moves to an "open" model governed by the Open-POWER Foundation. Material later in the preface identifies compliancy subsets of the architecture and the optional features which they comprise.

- The Power ISA Version 3.1 consists of three books and a set of appendices.

Book I, *Power ISA User Instruction Set Architecture*, covers the base instruction set and related facilities available to the application programmer.

Book II, Power ISA Virtual Environment Architecture, defines the storage model and other instructions and facilities that enable the application programmer to create multithreaded programs and programs that interact with certain physical realities of the computing environment.

Book III, *Power ISA Operating Environment Architecture*, defines the supervisor instructions and related facilities.

As used in this document, the term "Power ISA" refers to the instructions and facilities described in Books I, II, and III

Change bars have been included in the body of this document to indicate changes from the Power ISA Version 3.0C.

# **Summary of Changes in Power ISA Version 3.1**

This document is Version 3.1 of the Power ISA. It is intended to supersede and replace version 3.0C. Any product descriptions that reference a version of the architecture are understood to reference the latest version. This version was created by making miscellaneous corrections and by applying the following requests for change (RFCs) to Power ISA Version 3.0C. Change bars in this summary of changes indicate changes relative to v3.0C.

#### **Byte-Reverse Instructions:**

Added new GPR-based byte-reverse instructions.

#### Vector Integer Multiply/Divide/Modulo Instructions:

Added SIMD-equivalent forms of FXU multiply, divide, and modulo instructions to increase synergy with FXU instruction set for auto-vectorization.

#### Instruction Prefix Support:

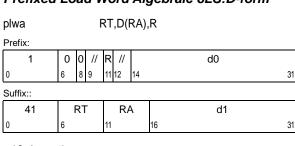

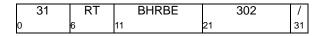

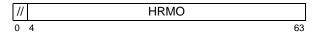

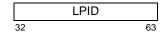

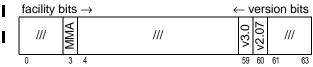

Added a 32-bit instruction prefix to support PC-relative addressing, up to 34-bit immediate operands, additional operand fields, and additional opcode space.

#### BHRB Filtering:

Added new BHRB Filtering fields and defined associated terminology.

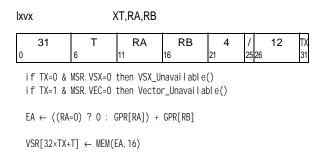

#### VSX 32-byte Storage Access Operations:

Added new 32-byte VSR load and store instructions.

#### Multiple DEAW:

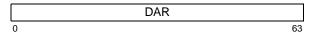

Added a second Data Address Watchpoint. [H]DAR is set to the first byte of overlap. 512B boundary is removed. Match detection is on DW granularity independent of operand size. SIAR/SDAR are not altered by the Trace interrupt when TE=0b00.

#### 128-bit Binary Integer Operations:

Added new 128-bit integer instructions for comparison, divide, modulo, rotate, shift, DFP and QFP format conversion operations. Also added 128-bit integer multiply assist operations.

#### SIMD Permute-Class Operations:

New permute-class instructions for element extraction and insertion operations, 32-bit immediate splat operations, doublewide bit shift left/right operations, element mask-based blend operations, and an arbitrary-wide permute assist operation.

### Reduced-Precision: Outer Product Operations:

Added new outer-product instructions to accelerate matrix multiplication, supporting 4-bit, 8-bit, and 16-bit integer and 16-bit, 32-bit, and 64-bit floating-point datatypes.

#### **Bit-Manipulation Operations:**

Added new bit-manipulation instructions.

#### Set Boolean Extension:

Added four new instructions that convert a condition code bit (any CR bit) into a Boolean (0/1), the negation of a Boolean (1/0), a field mask (all 0s/all 1s), and the negation of a field mask (all 1s/all 0s) that is placed into a GPR.

#### String Operations:

Added new string isolate instructions to support null-terminated and explicit-length strings.

#### Test LSB by Byte Operation:

Added new instruction to set any CR field to reflect predicate compare summary status, not just CR field 6 which Rc=1 is limited to.

#### VSX Load/Store Rightmost Element Operations:

Added new load and store instructions that transfer the rightmost vector element between VSR and storage.

#### <u>Prefixed addi Instruction and Prefixed Load/Store</u> Instructions and Addressing:

Using new instruction prefix, added support for extended immediate displacements and PC-relative addressing for a specific set of GPR and VSR load and store operations.

# VSX Scalar Minimum/Maximum/Compare Quad-Precision Operations:

Add new quad-precision minimum, maximum, and predicate comparison instructions.

# **CMODX Extension for Prefix:**

The quasi patch class of unsynchronized updates to instruction storage is made architecture. Language is changed and rules are added to account for the addition of prefixed instructions to the architecture.

# Reduced-Precision - bfloat16 Outer Product & Format Conversion Operations:

Added new instructions to accelerate matrix multiplication and format conversions for the bfloat16 datatype.

### Processor Control Register Extensions:

The PCR is updated to accommodate new problem-state instructions added in v3.1.

# Reduced-Precision: Missing Integer-based Outer Product Operations:

Added additional new instructions to accelerate matrix multiplication for 8-bit and 16-bit integer datatypes.

#### **VSX Mask Manipulation Operations:**

Added new vector instructions to manipulate vector masks.

#### VSX PCV Generate Operations:

Added new permute control vector generate instructions to support efficient emulation of load expand and store compress operations.

#### New Performance Monitor SPRs:

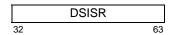

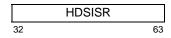

Added three new performance monitor SPRs. SIER2 and SIER3 are added to provide additional information about the sampled instruction. MMCR3 is added for further sampling related configuration control.

#### Translation Management Extensions:

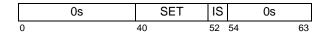

Added an L bit for slbiag, where L=1 indicates an invalidation by LPID. tlbiel with SET=0 and IS=1, 2, or 3 invalidate all congruence classes and tlbiel with SET !=0 is a noop except when RIC=1, which becomes an invalid form. Made ISL apply in hypervisor state.

#### Copy/Paste Extensions:

Added memory move functionality.

#### Persistent Storage / Store Sync:

Added pushes and synchronization for persistent storage and variants of sync optimized for store ordering.

#### Pause / Wait-reserve:

Added two new variants of the wait instruction; removed platform notify, TIDR, and CIR.

#### Performance Monitor Facility Sampling Security:

Changes the definition of MMCR0<sub>PMCC</sub>=0b00 case to allow for a new secure mode of access with regards to sampling registers which is available conditional on new MMCR<sub>PMCCEXT</sub> bit. Introduces a new freeze mode for ultravisor privilege state differentiating it from hypervisor privilege state freeze mode. Restricts BHRB to only record in problem state. Also MMCR0<sub>PMAQ</sub>, bit 52 of MMCR0 is removed.

#### **Hypervisor Interrupt Location Control:**

Added HAIL for the hypervisor to specify its interrupt behavior independent from guest state.

#### <u>Changes and Clarifications to Data Cache Mangement</u> Instructions:

Specifies the that the number of software data prefetch streams guaranteed to be available to a thread varies by degree of multithreading in the processor. Clarifies when a new software data prefetch stream will overwrite an existing one. Redefines when a thread's software data prefetch streams are cleared.

#### BHRB Disable Control:

Adds an additional control on BHRB recording via MMCRA bit 26 namely MMCRA  $_{\rm BHRBRD}.$

# **OpenISA Compliancy Subset Methodology and Requirements**

The PowerISA comprises the base architecture (that which is never optional - not part of any optional or deprecated feature), four groups of optional features, and a group of deprecated features. (See the next two pages.) Authorized implementations of the Power ISA must support one of the four Compliancy Subsets defined below. Support of a subset means that a design includes the base architecture and all features that are not optional for that subset. A supporting design may also include any features that are optional for the supported subset (including deprecated features), subject to stated pre-requisites, and Custom Extensions created using the architecture sandbox defined below. "Inclusion" of the base architecture, of an optional feature, or of a custom extension can be accomplished using a combination of hardware and firmware, provided that the firmware is implemented using other elements of the base architecture and of the included features, and elements of the architecture sandbox; invoked using the second and third pages of real storage (see the second bullet of Section 6.7.5 of Book III); and subject to the prohibitions against the use of firmware given in Section 7.4.4 of Book III. Each optional or deprecated feature must be implemented in its entirety. Attempted execution of an instruction associated with a feature that is not included must cause a Hypervisor Emulation Assistance Interrupt (HEAI). The result of an attempted access to an SPR associated with a feature that is not included using *mtspr* or *mfspr* must be that described for "an SPR number that is undefined for the implementation" in the respective instruction description. See Section 5.4.4 of Book III. For Scalar Fixed-Point + Floating-Point and Scalar Fixed-Point Compliancy Subset implementations that do not include the logical partitioning feature, an Illegal Instruction type Program Interrupt as described in the penultimate Programming Note in Section 7.5.9 of Book III may be substituted for the HEAI.

# **OpenPOWER Compliancy Subsets**

#### 1. AIX Compliancy Subset (ACS)

The following features are optional for this compliancy subset. The rest of PowerISA v3.1 must be included.

Always Optional Features listed below

Deprecated Features listed below

#### 2. Linux Compliancy Subset (LCS)

The following features are optional for this compliancy subset. The rest of PowerISA v3.1 must be included.

Linux Optional Features listed below

Always Optional Features listed below

Deprecated Features listed below

#### 3. Scalar Fixed-Point + Floating-Point Compliancy Subset (SFFS)

The following features are optional for this compliancy subset. The rest of PowerISA v3.1 must be included.

Scalar Float Optional Features listed below,

Linux Optional Features listed below

Always Optional Features listed below

Deprecated Features listed below

#### 4. Scalar Fixed-Point Compliancy Subset (SFS)

The following features are optional for this compliancy subset. The rest of PowerISA v3.1 must be included.

Scalar Fixed Optional Features listed below

Scalar Float Optional Features listed below

Linux Optional Features listed below

Always Optional Features listed below

Deprecated Features listed below

# **OpenPOWER Optional and Deprecated Features**

## **Always Optional Features**

The following features are optional for all compliancy subsets.

| Feature                                                                       | Reference                                                                                                          |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Copy/Paste for accelerator invocation and memory copy (CPA)                   | See Section 4.4 of Book II.                                                                                        |

| Secure Memory Facility (SMF) <sup>1</sup>                                     | See Chapter 3 of Book III.                                                                                         |

| Hardware and software data stream prefetching (STM) (DSCR state not optional) | See Section 4.2 and Section 4.3.2 of Book II.                                                                      |

| M=0 (M)<br>(non-coherent memory)                                              | See Section 1.6.3 of Book II.                                                                                      |

| W=1 (W)<br>(write through-required memory)                                    | See Section 1.6.1 of Book II.                                                                                      |

| Power management (PM) <sup>2</sup>                                            | See Section 4.2.2, Section 4.3.2, and the description of the PECE field(s) of the LPCR in Section 2.2 of Book III. |

| MMA <sup>3</sup>                                                              | See Section 7.2.1.3 and Section 7.6.1.12 of Book I.                                                                |

#### Notes:

- 1. LPAR is a pre-requisite for SMF.

- 2. If Power management is implemented by an ACS- or LCS-compliant design, it must be implemented as the architecture describes. If Power management is implemented by an SFFS- or SFS-compliant design, it need not be implemented as the architecture describes, and may include different interfaces created from the architecture sandbox.

- 3. SIMD is a requirement for MMA.

#### **Linux Optional Features**

The following features are optional for the Linux Compliancy Subset, the Scalar Fixed-Point + Floating-Point Compliancy Subset, and the Scalar Fixed-Point Compliancy Subset.

| Feature                                                                                                                               | Reference                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AIL/HAIL programmability (AIL) (AIL=3 and HAIL=1 required)                                                                            | See the description of the AIL and HAIL fields of the LPCR in Section 2.2 of Book III.                                                                                                                                |

| Atomic Memory Operations (AMO)                                                                                                        | See Section 4.5 of Book II.                                                                                                                                                                                           |

| Big Endian (BE) (LE is required for LCS. Linux supporting LCS is 64b LE Linux.)                                                       | See Section 1.10 of Book I and its first two subsections. Also see the description of the ILE field of the LPCR in Section 2.2 of Book III and the description of the LE bit of the MSR in Section 4.2.1 of Book III. |

| Branch History Rolling Buffer (BHRB)                                                                                                  | See Chapter 7 of Book II.                                                                                                                                                                                             |

| Decimal floating-point (DFP) <sup>1</sup>                                                                                             | See Chapter 5 of Book I.                                                                                                                                                                                              |

| Event-Based Branching (EBB)                                                                                                           | See Chapter 6 of Book II.                                                                                                                                                                                             |

| EVIRT programmability (EVIRT) <sup>2</sup> (EVIRT=1 required)                                                                         | See the description of the EVIRT field of the LPCR in Section 2.2 of Book III.                                                                                                                                        |

| SLB / HPT translation (HPT) (includes VPM, ISL, KBV)                                                                                  | See Section 6.7.7 through Section 6.7.9 of Book III. Also see the description of the VPM, ISL, and KBV fields of the LPCR in Section 2.2 of Book III.                                                                 |

| Load/Store Multiple instructions (LM)                                                                                                 | See Section 3.3.6 of Book I.                                                                                                                                                                                          |

| Load/Store String instructions (LS)                                                                                                   | See Section 3.3.7 of Book I.                                                                                                                                                                                          |

| Processor Compatibility Register (PCR) <sup>2</sup>                                                                                   | See Section 2.5 of Book III.                                                                                                                                                                                          |

| Quad-precision floating-point (QFP) <sup>3</sup>                                                                                      | See Chapter 7 of Book I.                                                                                                                                                                                              |

| Broadcast TLB shootdown (TLBIE) (tlbiel not optional)                                                                                 | See Section 6.9.3.3 of Book III.                                                                                                                                                                                      |

| Control Register (CTRL)                                                                                                               | See Section 5.3.4 of Book III.                                                                                                                                                                                        |

| SMT (SMT) <sup>4</sup> (includes PURR/SPURR, PSPB, RPR, PPR, processor control) (PPR and hypervisor/ultravior messaging not optional) | See Chapter 3 of Book II. Also see Section 5.3.5 through Section 5.3.7, Section 8.6, Section 8.7, and Chapter 11 of Book III.                                                                                         |

#### Notes:

- 1. FP is a pre-requisite for DFP.

- 2. LPAR is a pre-requisite for EVIRT and PCR.

- 3. SIMD is a pre-requisite for QFP.

- 4. If SMT is implemented by an LCS-compliant design, it must be implemented as the architecture describes. If SMT is not implemented by an LCS-compliant design, the design must not except on PPR accesses and must implement msgsnd[u], msgclr[u], and msgsync. If SMT is implemented by an SFFS- or SFS-compliant design, it need not be implemented as the architecture describes, and may include different interfaces created from the architecture sandbox.

## **Scalar Float Optional Features**

The following features are optional for the Scalar Fixed-Point + Floating-Point Compliancy Subset and the Scalar Fixed-Point Compliancy Subset.

| Feature                                                                                                                                         | Reference                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIMD (SIMD) <sup>1</sup><br>(VMX and VSX)                                                                                                       | See Chapter 6 and Chapter 7 of Book I.                                                                                                                                                                                |

| SF=1 (64-bit) <sup>2</sup>                                                                                                                      | See Section 1.5 and Section 1.10.3 of Book I and the description of the SF field of the MSR in Section 4.2.1 of Book III.                                                                                             |

|                                                                                                                                                 | See Section 1.10 of Book I and its first two subsections. Also see the description of the ILE field of the LPCR in Section 2.2 of Book III and the description of the LE bit of the MSR in Section 4.2.1 of Book III. |

| Logical partitioning (LPAR) <sup>3,4</sup>                                                                                                      | See Chapter 2 of Book III.                                                                                                                                                                                            |

| Fixed-point instructions that modify OV to indicate whether overflow occurred (OV) (addex and instructions with OE=1 such as addo, subfo, etc.) |                                                                                                                                                                                                                       |

| Nested radix translation (ROR) <sup>5</sup> (single-level radix translation not optional)                                                       | See Section 6.7.7 and Section 6.7.10 of Book III.                                                                                                                                                                     |

#### Notes:

- 1. FP is a pre-requisite for SIMD.

- 2. When 64-bit is not included, a single radix tree will be used to map both application and OS address spaces (no quadrant structure).

- 3. 64-bit is a pre-requisite for LPAR.

- 4. When LPAR is not included, MSR<sub>HV</sub>=1 always.

- 5. LPAR is a pre-requisite for ROR.

#### **Scalar Fixed Optional Features**

The following features are optional for the Scalar Fixed-Point Compliancy Subset

| Feature                           | Reference                |

|-----------------------------------|--------------------------|

| Scalar binary floating-point (FP) | See Chapter 4 of Book I. |

#### **Deprecated Features**

There are no deprecated features in Power ISA v3.1.

# **OpenPOWER Architecture Sandbox**

OpenPOWER compliancy subsets permit Custom Extensions. Any architectural resources used for Custom Extensions must use only the resources described below and any instructions and SPRs that the architecture describes as implementation-dependent.

Development of Custom Extensions using the architecture sandbox is appropriate for facilities that benefit a small portion of the processor design space. For facilities with broad applicability, developers are strongly encouraged to submit a proposal for adoption into the architecture. Adopted proposals will become optional or required features of the architecture, and will be assigned resources that are not in the architecture sandbox to avoid fragmentation of the architecture. Facilities described in proposals that are not adopted into the architecture may be implemented as Custom Extensions using the architecture sandbox.

System software and toolchain support of Custom Extensions is not guaranteed. Developers are encouraged to provide a means to disable custom extensions to present an architecture that is supported by standard system software and toolchain.

The architecture sandbox consists of the following.

- The designated opcode sandbox is instructions having a primary opcode of 22. Note that primary opcode 22 is reserved by AIX. As a result, Custom Extensions that use primary opcode 22 are not compatible with ACS.

- The designated SPR sandbox consists of non-privileged SPRs 704-719 and privileged SPRs 720-735.

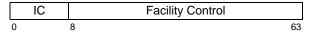

- The designated [H]FSCR sandbox consists of [H]FSCR bits 8-9 and their corresponding IC values.

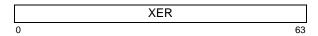

- The designated XER bit sandbox consists of XER bits 54:55.

- The designated FPSCR bit sandbox consists of FPSCR bits 14-15.

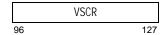

- The designated VSCR bit sandbox consists of VSCR bits 96 & 112. VSCR bit 96 is provided for Vector Facility control & VSCR bit 112 is provided for Vector Facility status.

- The designated interrupt vector sandbox consists of interrupt vector 0x0000\_0000\_0000\_0FE0.

# **Table of Contents**

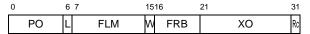

|                                              | 1.6.1.16 XFL-FORM                          |

|----------------------------------------------|--------------------------------------------|

|                                              | 1.6.1.17 XFX-FORM 15                       |

| Prefacev                                     | 1.6.1.18 XL-FORM                           |

| Summary of Changes in Power ISA Ver-         | 1.6.1.19 XO-FORM15                         |

| sion 3.1 vi                                  | 1.6.1.20 XS-FORM                           |

| OpenISA Compliancy Subset Methodol-          | 1.6.1.21 XX2-FORM                          |

| ogy and Requirements viii                    | 1.6.1.22 XX3-FORM                          |

| 3, 4 4 4 4 4                                 | 1.6.1.23 XX4-FORM 15                       |

| Table of Contents xiii                       | 1.6.1.24 Z22-FORM                          |

| Table of Comonic IIIIIIIIIIIIIIIIII          | 1.6.1.25 Z23-FORM 16                       |

| Dook I.                                      | 1.6.2 Word Instruction Fields 16           |

| Book I:                                      | 1.6.3 Instruction Prefix Formats 22        |

|                                              | 1.6.3.1 Type 00 Prefix – Eight-Byte Load/  |

| Power ISA User Instruction Set               | Store Instructions22                       |

| Architecture1                                | 1.6.3.2 Type 01 Prefix – Eight-Byte Regis- |

| Aiomicotaiciiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiii | ter-to-Register Instructions 23            |

| Chapter 4 Introduction 2                     | 1.6.3.3 Type 10 - Modified Load/Store      |

| Chapter 1. Introduction 3                    | Instructions                               |

| 1.1 Overview                                 | 1.6.3.4 Type 11 - Modified Regis-          |

| 1.2 Instruction Mnemonics and Operands3      | ter-to-Register Instructions 23            |

| 1.3 Document Conventions 3                   | 1.6.4 Instruction Prefix Fields 23         |

| 1.3.1 Definitions                            | 1.7 Classes of Instructions 24             |

| 1.3.2 Notation 4                             | 1.7.1 Defined Instruction Class 24         |

| 1.3.3 Reserved Fields, Reserved Values,      | 1.7.2 Illegal Instruction Class 24         |

| and Reserved SPRs 5                          | 1.7.3 Reserved Instruction Class 24        |

| 1.3.4 Description of Instruction Operation 6 | 1.8 Forms of Defined Instructions 24       |

| 1.3.5 Phased-Out Facilities 8                | 1.8.1 Preferred Instruction Forms 24       |

| 1.4 Processor Overview 9                     | 1.8.2 Invalid Instruction Forms 24         |

| 1.5 Computation modes                        | 1.8.3 Reserved-no-op Instructions 25       |

| 1.6 Instruction Formats                      | 1.9 Exceptions                             |

| 1.6.1 Word Instruction Formats 12            | 1.10 Storage Addressing                    |

| 1.6.1.1 A-FORM                               | 1.10.1 Storage Operands                    |

| 1.6.1.2 B-FORM                               | 1.10.2 Instruction Fetches                 |

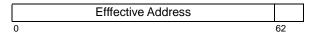

| 1.6.1.3 D-FORM                               | 1.10.3 Effective Address Calculation 29    |

| 1.6.1.4 DQ-FORM                              |                                            |

| 1.6.1.6 DX-FORM                              | Chapter 2. Branch Facility                 |

| 1.6.1.7 I-FORM                               | 2.1 Branch Facility Overview33             |

| 1.6.1.8 M-FORM                               | 2.2 Instruction Execution Order 33         |

| 1.6.1.9 MD-FORM                              | 2.3 Branch Facility Registers 34           |

| 1.6.1.10 MDS-FORM                            | 2.3.1 Condition Register 34                |

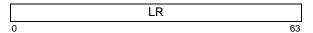

| 1.6.1.11 SC-FORM                             | 2.3.2 Link Register                        |

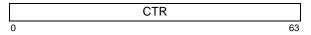

| 1.6.1.12 VA-FORM                             | 2.3.3 Count Register                       |

| 1.6.1.13 VC-FORM                             | 2.3.4 Target Address Register35            |

| 1.6.1.14 VX-FORM                             | 2.4 Branch Instructions 37                 |

| 1.6.1.15 X-FORM                              | 2.5 Condition Register Instructions 44     |

| 2.5.1 Condition Register Logical Instruc-     | 3.3.14.2.1 64-bit Fixed-Point Shift Instruc-          |

|-----------------------------------------------|-------------------------------------------------------|

| tions                                         | tions                                                 |

| 2.5.2 Condition Register Field Instruction .  | 3.3.15 Binary Coded Decimal (BCD)                     |

| 46                                            | Assist Instructions                                   |

| 2.6 System Call Instructions 47               | 3.3.16 Byte-Reverse Instructions 119                  |

|                                               | 3.3.17 Move To/From Vector-Scalar Regis-              |

| Chapter 3. Fixed-Point Facility 49            | ter Instructions 120                                  |

| 3.1 Fixed-Point Facility Overview 49          | 3.3.18 Move To/From System Register                   |

| 3.2 Fixed-Point Facility Registers 49         | Instructions                                          |

| 3.2.1 General Purpose Registers49             | 3.3.19 Prefixed No-Operation Instruction.             |

| 3.2.2 Fixed-Point Exception                   | 130                                                   |

| Register                                      |                                                       |

| 3.2.3 VR Save Register                        | Chapter 4. Floating-Point Facility 131                |

| 3.3 Fixed-Point Facility Instructions 51      | 4.1 Floating-Point Facility Overview 131              |

| 3.3.1 Fixed-Point Storage Access Instruc-     | 4.2 Floating-Point Facility Registers 132             |

| tions                                         | 4.2.1 Floating-Point Registers 132                    |

| 3.3.1.1 Storage Access Exceptions51           | 4.2.2 Floating-Point Status and Control               |

| 3.3.2 Fixed-Point Load Instructions51         | Register132                                           |

| 3.3.2.1 64-bit Fixed-Point Load Instruc-      | 4.3 Floating-Point Data                               |

| tions56                                       | 4.3.1 Data Format                                     |

| 3.3.3 Fixed-Point Store Instructions 58       | 4.3.2 Value Representation                            |

| 3.3.3.1 64-bit Fixed-Point Store Instruc-     | 4.3.3 Sign of Result                                  |

| tions                                         | 4.3.4 Normalization and                               |

| 3.3.4 Fixed Point Load and Store Quad-        | Denormalization                                       |

| word Instructions                             | 4.3.5 Data Handling and Precision 137                 |

| 3.3.5 Fixed-Point Load and Store with Byte    |                                                       |

| Reversal Instructions                         | 4.3.5.1 Single-Precision Operands 137                 |

|                                               | 4.3.5.2 Integer-Valued Operands 138<br>4.3.6 Rounding |

| 3.3.5.1 64-Bit Load and Store with Byte       |                                                       |

| Reversal Instructions                         | 4.4 Floating-Point Exceptions 140                     |

| 3.3.6 Fixed-Point Load and Store Multiple     | 4.4.1 Invalid Operation Exception 142                 |

| Instructions                                  | 4.4.1.1 Definition                                    |

| 3.3.7 Fixed-Point Move Assist Instructions    | 4.4.1.2 Action                                        |

| [Phased Out]71                                | 4.4.2 Zero Divide Exception 142                       |

| 3.3.8 Other Fixed-Point Instructions74        | 4.4.2.1 Definition                                    |

| 3.3.9 Fixed-Point Arithmetic Instructions 75  | 4.4.2.2 Action                                        |

| 3.3.9.1 64-bit Fixed-Point Arithmetic         | 4.4.3 Overflow Exception                              |

| Instructions                                  | 4.4.3.1 Definition                                    |

| 3.3.10 Fixed-Point Compare Instructions       | 4.4.3.2 Action                                        |

| 92                                            | 4.4.4 Underflow Exception 144                         |

| 3.3.10.1 Character-Type Compare Instruc-      | 4.4.4.1 Definition                                    |

| tions                                         | 4.4.4.2 Action                                        |

| 3.3.11 Fixed-Point Trap Instructions96        | 4.4.5 Inexact Exception 144                           |

| 3.3.11.1 64-bit Fixed-Point Trap Instruc-     | 4.4.5.1 Definition                                    |

| tions                                         | 4.4.5.2 Action                                        |

| 3.3.12 Fixed-Point Select98                   | 4.5 Floating-Point Execution Models . 145             |

| 3.3.13 Fixed-Point Logical Instructions .99   | 4.5.1 Execution Model for IEEE Opera-                 |

| 3.3.13.1 64-bit Fixed-Point Logical Instruc-  | tions                                                 |

| tions                                         | 4.5.2 Execution Model for                             |

| 3.3.14 Fixed-Point Rotate and Shift           | Multiply-Add Type Instructions 147                    |

| Instructions                                  | 4.6 Floating-Point Facility Instructions 148          |

| 3.3.14.1 Fixed-Point Rotate Instructions      | 4.6.1 Floating-Point Storage Access                   |

| 107                                           | Instructions                                          |

| 3.3.14.1.1 64-bit Fixed-Point Rotate          | 4.6.1.1 Storage Access Exceptions 148                 |

| Instructions110                               | 4.6.2 Floating-Point Load Instructions 149            |

| 3.3.14.2 Fixed-Point Shift Instructions . 113 | 4.6.3 Floating-Point Store Instructions 154           |

| 4.6.4 Floating-Point Load and Store Dou-      | 5.5.10.3 Overflow Exception 201                                        |

|-----------------------------------------------|------------------------------------------------------------------------|

| ble Pair Instructions [Phased-Out] 159        | 5.5.10.4 Underflow Exception 201                                       |

| 4.6.5 Floating-Point Move Instructions 161    | 5.5.10.5 Inexact Exception 202                                         |

| 4.6.6 Floating-Point Arithmetic Instructions  | 5.5.11 Summary of Normal Rounding And                                  |

| 163                                           | Range Actions                                                          |

| 4.6.6.1 Floating-Point Elementary Arithme-    | 5.6 DFP Instruction Descriptions 205                                   |

| tic Instructions                              | 5.6.1 DFP Arithmetic Instructions 205                                  |

|                                               | 5.6.2 DFP Compare Instructions210<br>5.6.3 DFP Test Instructions213    |

| tions                                         |                                                                        |

|                                               | 5.6.4 DFP Quantum Adjustment Instruc-                                  |

| version Instructions                          | tions                                                                  |

| tion                                          | 5.6.5.1 DFP Data-Format Conversion                                     |

| 4.6.7.2 Floating-Point Convert To/From        | Instructions                                                           |

| Integer Instructions                          | 5.6.5.2 DFP Data-Type Conversion                                       |

| 4.6.7.3 Floating Round to Integer Instruc-    | Instructions                                                           |

| tions                                         | 5.6.6 DFP Format Instructions 235                                      |

| 4.6.8 Floating-Point Compare Instructions 179 | 5.6.7 DFP Instruction Summary 239                                      |

| 4.6.9 Floating-Point Select Instruction 180   | Chapter 6. Vector Facility 243                                         |

| 4.6.10 Floating-Point Status and Control      | 6.1 Vector Facility Overview 243                                       |

| Register Instructions 182                     | 6.2 Chapter Conventions 243                                            |

| -                                             | 6.2.1 Description of Instruction Operation.                            |

| Chapter 5. Decimal Floating-Point             | 243                                                                    |

| 187                                           | 6.3 Vector Facility Registers 258                                      |

| 5.1 Decimal Floating-Point (DFP) Facility     | 6.3.1 Vector-Scalar Registers 258                                      |

| Overview                                      | 6.3.2 Vector Status and Control Register .                             |

| 5.2 DFP Register Handling 188                 | 258                                                                    |

| 5.2.1 DFP Usage of Floating-Point Regis-      | 6.3.3 VR Save Register 259                                             |

| ters                                          | 6.4 Vector Storage Access Operations 260                               |

| 5.3 DFP Support for Non-DFP Data Types        | 6.4.1 Accessing Unaligned Storage Oper-                                |

| 190                                           | ands262                                                                |

| 5.4 DFP Number Representation 191             | 6.5 Vector Integer Operations 263                                      |

| 5.4.1 DFP Data Format 191                     | 6.5.1 Integer Saturation 264                                           |

| 5.4.1.1 Fields Within the Data Format 191     | 6.6 Vector Floating-Point Operations . 265                             |

| 5.4.1.2 Summary of DFP Data Formats           | 6.6.1 Floating-Point Overview 265                                      |

| 192                                           | 6.6.2 Floating-Point Exceptions 265                                    |

| 5.4.1.3 Preferred DPD Encoding 193            | 6.6.2.1 NaN Operand Exception 265                                      |

| 5.4.2 Classes of DFP Data 193                 | 6.6.2.2 Invalid Operation Exception 266                                |

| 5.5 DFP Execution Model 194                   | 6.6.2.3 Zero Divide Exception 266<br>6.6.2.4 Log of Zero Exception 266 |

| 5.5.1 Rounding                                | 6.6.2.5 Overflow Exception 266                                         |

| 5.5.2 Rounding Mode Specification 195         | 6.6.2.6 Underflow Exception 266                                        |

| 5.5.3 Formation of Final Result 195           | 6.7 Vector Storage Access Instructions 267                             |

| 5.5.3.1 Use of Ideal Exponent 195             | 6.7.1 Storage Access Exceptions 267                                    |

| 5.5.4 Arithmetic Operations 196               | 6.7.2 Vector Load Instructions 268                                     |

| 5.5.4.1 Sign of Arithmetic Result 196         | 6.7.3 Vector Store Instructions 272                                    |

| 5.5.5 Compare Operations                      | 6.7.4 Vector Alignment Support Instruc-                                |

| 5.5.7 Quantum Adjustment Operations 196       | tions                                                                  |

| 5.5.8 Conversion Operations 197               | 6.8 Vector Permute and Formatting                                      |

| 5.5.8.1 Data-Format Conversion 197            | Instructions                                                           |

| 5.5.8.2 Data-Type Conversion 197              | 6.8.1 Vector Pack Instructions 278                                     |

| 5.5.9 Format Operations 197                   | 6.8.2 Vector Unpack Instructions 285                                   |

| 5.5.10 DFP Exceptions                         | 6.8.3 Vector Merge Instructions 289                                    |

| 5.5.10.1 Invalid Operation Exception . 199    | 6.8.4 Vector Splat Instructions 293                                    |

| 5.5.10.2 Zero Divide Exception 200            | 6.8.5 Vector Permute Instruction 296                                   |

| 6.8.6 Vector Select Instruction                 | 6.9.3 Vector Integer Compare Instructions                                                                |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 6.8.7 Vector Shift Instructions                 | 388                                                                                                      |

| 6.8.8 Vector Extract Element Instructions . 304 | <ul><li>6.9.4 Vector Logical Instructions 402</li><li>6.9.5 Vector Integer Rotate Instructions</li></ul> |

| 6.8.8.1 Vector Extract Element to VSR           | 404                                                                                                      |

| using Immediate-specified Index Instructions    | 6.9.5.1 Vector Integer Rotate Left Instructions                                                          |

|                                                 |                                                                                                          |

| 6.8.8.2 Vector Extract Element to GPR           | 6.9.5.2 Vector Integer Rotate Left then                                                                  |

| using GPR-specified Index Instructions 306      | AND with Mask Instructions 407                                                                           |

| 6.8.8.3 Vector Extract Double Element to        | 6.9.5.3 Vector Integer Rotate Left then                                                                  |

| VSR Using GPR-specified Index Instruc-          | Mask Insert Instructions 410                                                                             |

| tions                                           | 6.9.6 Vector Integer Shift Instructions. 413                                                             |

| 6.8.9 Vector Insert Element Instructions        | 6.9.6.1 Vector Integer Shift Left Instruc-                                                               |

| 313                                             | tions                                                                                                    |

| 6.8.9.1 Vector Insert Element from VSR          | 6.9.6.2 Vector Integer Shift Right Instruc-                                                              |

| Using Immediate-specified Index Instruc-        | tions                                                                                                    |

| tions                                           | 6.9.6.3 Vector Integer Shift Right Algebraic                                                             |

| 6.8.9.2 Vector Insert Element from GPR          | Instructions 419                                                                                         |

| Using GPR-specified Index Instructions          | 6.10 Vector Floating-Point Instruction Set                                                               |

| 315                                             | 422                                                                                                      |

| 6.8.9.3 Vector Insert Element from GPR          | 6.10.1 Vector Floating-Point Arithmetic                                                                  |

|                                                 | Instructions                                                                                             |

| Using Immediate-specified Index Instruc-        |                                                                                                          |

| tions                                           | 6.10.2 Vector Floating-Point Maximum/                                                                    |

| 6.8.9.4 Vector Insert Element from VSR          | Minimum Instructions 424                                                                                 |

| Using GPR-specified Index Instructions          | 6.10.3 Vector Floating-Point Rounding and                                                                |

| 320                                             | Conversion Instructions 425                                                                              |

| 6.9 Vector Integer Instructions 323             | 6.10.3.1 Vector Floating-Point Conversion                                                                |

| 6.9.1 Vector Integer Arithmetic Instructions    | Instructions 425                                                                                         |

| 323                                             | 6.10.3.2 Vector Floating-Point Round to                                                                  |

| 6.9.1.1 Vector Integer Add Instructions 323     | Integral Instructions                                                                                    |

| 6.9.1.2 Vector Integer Subtract Instructions    | 6.10.4 Vector Floating-Point Compare                                                                     |

| 331                                             | Instructions 429                                                                                         |

| 6.9.1.3 Vector Integer Multiply Instructions    | 6.10.5 Vector Floating-Point Estimate                                                                    |

| 339                                             | Instructions                                                                                             |

| 6.9.1.4 Vector Integer Multiply-Add/Sum         | 6.11 Vector Exclusive-OR-based Instruc-                                                                  |

| Instructions                                    | tions                                                                                                    |

| 6.9.1.5 Vector Integer Divide Instructions .    | 6.11.1 Vector AES Instructions 435                                                                       |

| 358                                             | 6.11.2 Vector SHA-256 and SHA-512                                                                        |

| 6.9.1.6 Vector Integer Modulo Instructions.     | Sigma Instructions 438                                                                                   |

| 364                                             | 6.11.3 Vector Binary Polynomial Multiplica-                                                              |

| 6.9.1.7 Vector Integer Sum-Across Instruc-      | tion Instructions                                                                                        |

| tions                                           | 6.11.4 Vector Permute & Exclusive-OR                                                                     |

|                                                 |                                                                                                          |

| 6.9.1.8 Vector Integer Negate Instructions.     | Instruction                                                                                              |

| 371                                             | 6.12 Vector Bit Manipulation Instructions .                                                              |

| 6.9.1.9 Vector Extend Sign Instructions         | 445                                                                                                      |

| 372                                             | 6.12.1 Vector Gather Bits Instructions 445                                                               |

| 6.9.1.10 Vector Integer Average Instruc-        | 6.12.2 Vector Count Leading Zeros                                                                        |

| tions                                           | Instructions 447                                                                                         |

| 6.9.1.11 Vector Integer Absolute Differ-        | 6.12.3 Vector Count Trailing Zeros Instruc-                                                              |

| ence Instructions                               | tions                                                                                                    |

| 6.9.2 Vector Integer Maximum/Minimum            | 6.12.4 Vector Count Leading/Trailing Zero                                                                |

| Instructions                                    | LSB Instructions 453                                                                                     |

| 6.9.2.1 Vector Integer Maximum Instruc-         | 6.12.5 Vector Bit Insert/Extract Instructions                                                            |

| tions                                           | 454                                                                                                      |

| 6.9.2.2 Vector Integer Minimum Instruc-         | 6.12.6 Vector Centrifuge Instruction 456                                                                 |

| tions 004                                       | 5210 Toolor Continued mondonon 1 400                                                                     |

| 6.12.7 Vector Population Count Instruc-     | 7.3.1 VSX Floating-Point Arithmetic Over-  |

|---------------------------------------------|--------------------------------------------|

| tions                                       | view                                       |

| 6.12.8 Vector Parity Byte Instructions. 459 | 7.3.2 VSX Floating-Point Data 509          |

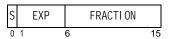

| 6.12.9 Vector Bit Permute Instructions 461  | 7.3.2.1 Data Format 509                    |

| 6.13 Vector Mask Manipulation Instruc-      | 7.3.2.2 Value Representation 511           |

| tions                                       | 7.3.2.3 Sign of Result 512                 |

| 6.13.1 Vector Mask Move Instructions 463    | 7.3.2.4 Normalization and Denormalization  |

| 6.13.2 Vector Expand Mask Instructions .    | 513                                        |

| 466                                         | 7.3.2.5 Data Handling and Precision 513    |

| 6.13.3 Vector Count Mask Bits Instructions  | 7.3.2.6 Rounding                           |

| 469                                         | 7.3.3 VSX Floating-Point Execution Mod-    |

| 6.13.4 Vector Extract Mask Instructions     | <del>_</del>                               |

|                                             | els                                        |

| 471                                         | 7.3.3.1 VSX Execution Model for IEEE       |

| 6.14 Vector String Instructions 474         | Operations                                 |

| 6.14.1 Vector String Isolate Instructions   | 7.3.3.2 VSX Execution Model for Multi-     |

| 474                                         | ply-Add Type Instructions 522              |

| 6.14.2 Vector Clear Bytes Instructions 476  | 7.4 VSX Floating-Point Exceptions 524      |

| 6.15 Decimal Integer Instructions 477       | 7.4.1 Floating-Point Invalid Operation     |

| 6.15.1 Decimal Integer Arithmetic Instruc-  | Exception527                               |

| tions 477                                   | 7.4.1.1 Definition 527                     |

| 6.15.2 Decimal Integer Format Conversion    | 7.4.1.2 Action for VE=1                    |

| Instructions                                | 7.4.1.3 Action for VE=0530                 |

| 6.15.3 Decimal Integer Sign Manipulation    | 7.4.2 Floating-Point Zero Divide Exception |

| Instructions 489                            | 539                                        |

| 6.15.4 Decimal Integer Shift and Round      | 7.4.2.1 Definition 539                     |

| Instructions 491                            | 7.4.2.2 Action for ZE=1 539                |

| 6.15.5 Decimal Integer Truncate Instruc-    | 7.4.2.3 Action for ZE=0 540                |

| tions 494                                   | 7.4.3 Floating-Point Overflow Exception    |

| 6.16 Vector Status and Control Register     | 542                                        |

| Instructions 496                            | 7.4.3.1 Definition 542                     |

|                                             | 7.4.3.2 Action for OE=1                    |

| Chapter 7. Vector-Scalar Extension          | 7.4.3.3 Action for OE=0545                 |

|                                             | 7.4.4 Floating-Point Underflow Exception.  |

| Facility 497                                | 548                                        |

| 7.1 Introduction                            | 7.4.4.1 Definition 548                     |

| 7.1.1 Overview of the Vector-Scalar Exten-  | 7.4.4.2 Action for UE=1548                 |

| sion                                        | 7.4.4.3 Action for UE=0                    |

| 7.1.1.1 Combining the Floating-Point Reg-   | 7.4.5 Floating-Point Inexact Exception 554 |

| isters (FPR) defined in Chapter 4 Float-    | 7.4.5.1 Definition                         |

| ing-Point Facility and the Vector Registers | 7.4.5.1 Definition                         |

| (VR) defined in Chapter 6 Vector Facility   | 7.4.5.2 Action for XE=1                    |

| provides additional registers to support    |                                            |

| more aggressive compiler optimizations for  | 7.5 VSX Storage Access Operations . 561    |

| both vector and scalar operations.Compat-   | 7.5.1 Accessing Aligned Storage Oper-      |

| ibility with Floating-Point and Decimal     | ands561                                    |

| Floating-Point Operations 497               | 7.5.2 Accessing Unaligned Storage Oper-    |

| 7.1.1.2 Compatibility with Vector Opera-    | ands                                       |

| tions                                       | 7.5.3 Storage Access Exceptions 563        |

| 7.2 VSX Registers 498                       | 7.6 VSX Instruction Set 564                |

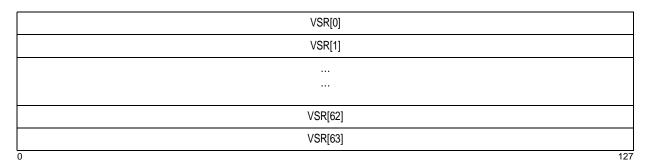

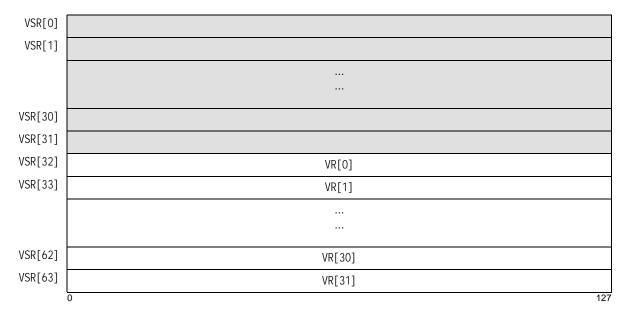

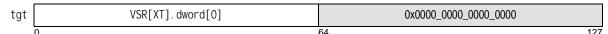

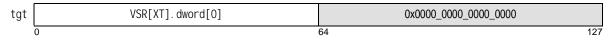

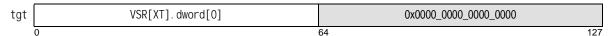

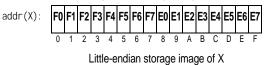

| 7.2.1 Vector-Scalar Registers 498           | 7.6.1 VSX Instruction Set Summary 564      |

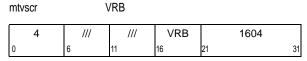

|                                             | 7.6.1.1 VSX Storage Access Instructions .  |

| 7.2.1.1 Floating-Point Registers 498        | 564                                        |

| 7.2.1.2 Vector Registers 500                | 7.6.1.2 VSX Binary Floating-Point Sign     |

| 7.2.1.3 VSX Accumulators 501                | Manipulation Instructions 567              |

| 7.2.2 Floating-Point Status and Control     | 7.6.1.3 VSX Binary Floating-Point Arithme- |

| Register                                    | tic Instructions                           |

| 7.3 VSX Operations 508                      |                                            |

| 7.6.1.4 VSX Binary Floating-Point Com-                                         | Appendix C. Assembler Extended                                                                                                                                                                        |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pare Instructions                                                              | Mnemonics                                                                                                                                                                                             |

| 7.6.1.5 VSX Binary Floating-Point Round                                        | C.1 Symbols 1011                                                                                                                                                                                      |

| to Shorter Precision Instructions 571                                          | C.2 Branch Mnemonics 1012                                                                                                                                                                             |

| 7.6.1.6 VSX Binary Floating-Point Convert                                      | C.2.1 BO and BI Fields 1012                                                                                                                                                                           |

| to Shorter Precision Instructions 571                                          | C.2.2 Simple Branch Mnemonics 1012                                                                                                                                                                    |

| 7.6.1.7 VSX Binary Floating-Point Convert                                      | C.2.3 Branch Mnemonics Incorporating                                                                                                                                                                  |

| to Longer Precision Instructions 571                                           | Conditions                                                                                                                                                                                            |

| 7.6.1.8 VSX Binary Floating-Point Round                                        | C.2.4 Branch Prediction 1014                                                                                                                                                                          |

| to Integral Instructions                                                       | C.3 Condition Register Logical Mnemonics                                                                                                                                                              |

| 7.6.1.9 VSX Binary Floating-Point Convert                                      | 1015                                                                                                                                                                                                  |

| To Integer Instructions                                                        | C.4 Subtract Mnemonics 1015                                                                                                                                                                           |

| 7.6.1.10 VSX Binary Floating-Point Con-                                        | C.4.1 Subtract Immediate 1015                                                                                                                                                                         |

| vert From Integer Instructions                                                 | C.4.2 Subtract                                                                                                                                                                                        |

| 7.6.1.11 VSX Binary Floating-Point Math                                        | C.5 Compare Mnemonics 1016                                                                                                                                                                            |

| Support Instructions                                                           | C.5.1 Doubleword Comparisons 1016                                                                                                                                                                     |

| 7.6.1.12 VSX Matrix-Multiply Assist (MMA)                                      | C.5.2 Word Comparisons 1016                                                                                                                                                                           |

| Instructions                                                                   | C.6 Trap Mnemonics 1017                                                                                                                                                                               |

| 7.6.1.12.1 VSX Accumulator Move Instruc-                                       | C.7 Integer Select Mnemonics 1018                                                                                                                                                                     |

| tions                                                                          | C.8 Rotate and Shift Mnemonics 1019                                                                                                                                                                   |

| 7.6.1.12.2 VSX Binary Integer Outer-Prod-                                      | C.8.1 Operations on Doublewords 1019                                                                                                                                                                  |

| uct Instructions                                                               | C.8.2 Operations on Words 1020                                                                                                                                                                        |

| Outer-Product Instructions                                                     | C.9 Move To/From Special Purpose Regis-                                                                                                                                                               |

| 7.6.1.13 VSX Vector Logical Instructions                                       | ter Mnemonics 1021                                                                                                                                                                                    |

| 576                                                                            | C.10 Miscellaneous Mnemonics 1022                                                                                                                                                                     |

| 7.6.1.14 VSX Vector Permute-class                                              | Book II:                                                                                                                                                                                              |

| Instructions                                                                   | BOOK II.                                                                                                                                                                                              |

| 7.6.1.15 VSX Vector Load Special Value                                         |                                                                                                                                                                                                       |

| Instruction                                                                    | Power ISA Virtual Environment                                                                                                                                                                         |

| 7.6.1.16 VSX Vector Test Least-Signifi-                                        | Architecture 1027                                                                                                                                                                                     |

| cant Bit by Byte Instruction                                                   |                                                                                                                                                                                                       |

| 7.6.2 VSX Instruction Description Conven-                                      | Chapter 1. Storage Model 1029                                                                                                                                                                         |

| tions                                                                          | 1.1 Definitions                                                                                                                                                                                       |

| 7.6.2.1 VSX Instruction RTL Operators 579 7.6.2.2 VSX Instruction RTL Function | 1.2 Introduction                                                                                                                                                                                      |

| Calls                                                                          | 1.3 Virtual Storage                                                                                                                                                                                   |

| 7.6.3 VSX Instruction Descriptions 610                                         | 1.4 Single-Copy Atomicity 1031                                                                                                                                                                        |

| 7.0.0 VOX Instruction Descriptions                                             | 1.5 Cache Model                                                                                                                                                                                       |

| Appendix A. Suggested                                                          | 1.6 Storage Control Attributes 1032                                                                                                                                                                   |

|                                                                                | 1.6.1 Write Through Required 1033                                                                                                                                                                     |

| Floating-Point Models995                                                       | 1.6.2 Caching Inhibited 1033                                                                                                                                                                          |

| A.1 Floating-Point Round to Single-Preci-                                      | 1.6.3 Memory Coherence Required 1033                                                                                                                                                                  |

| sion Model                                                                     | 1.6.4 Guarded                                                                                                                                                                                         |

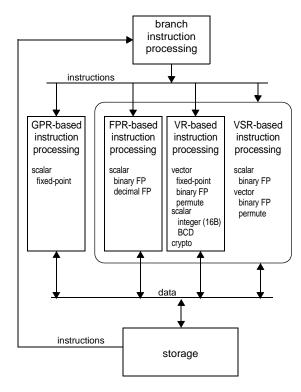

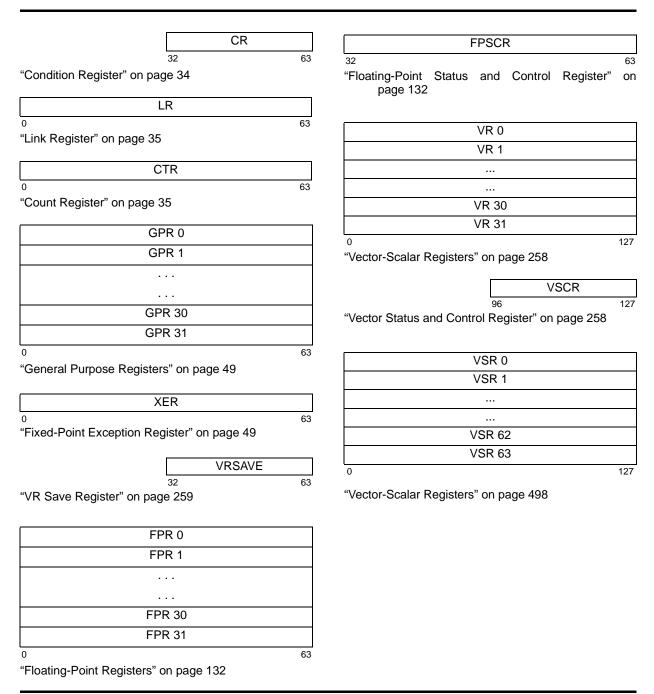

| A.2 Floating-Point Convert to Integer                                          | 1.7 Shared Storage 1034                                                                                                                                                                               |